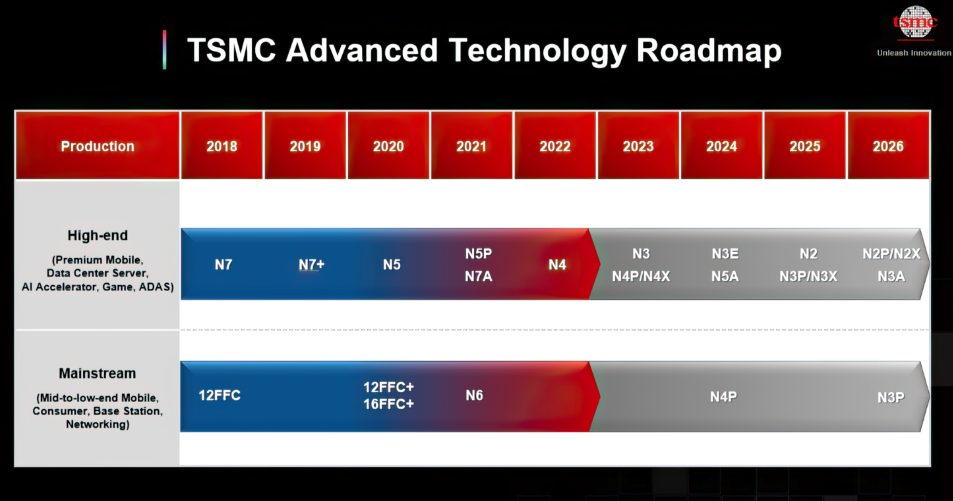

Ang ikatlong henerasyon ng TSMC na 3nm node

Matagumpay na sinimulan ng TSMC ang paggamit ng teknolohiyang proseso ng pangalawang henerasyon na 3NM upang makabuo ng mga chips sa ika-apat na quarter ng 2023, nakamit ang nakaplanong milyahe.Kasalukuyang naghahanda ang kumpanya sa masa na gawa ng pagganap na pinahusay na N3P chips para sa node na ito.Inihayag ng TSMC sa European Technology Symposium na magaganap ito sa ikalawang kalahati ng 2024.

Ang proseso ng N3E ay nagpasok ng mass production tulad ng naka -iskedyul, at ang density ng depekto ay maihahambing sa proseso ng N5 sa panahon ng paggawa ng masa noong 2020. Inilarawan ng TSMC ang ani ng N3E bilang "mahusay", at sa kasalukuyan ang nag -iisang processor na gumagamit ng N3E - Apple M4- ay may makabuluhangnadagdagan ang bilang ng mga transistor at bilis ng orasan ng orasan kumpara sa M3 batay sa teknolohiya ng N3.

Sinabi ng isang executive ng TSMC sa kaganapan, "Sinimulan ng N3E ang paggawa ng masa tulad ng pinlano sa ika -apat na quarter ng nakaraang taon. Nakita namin ang mahusay na pagganap ng produksyon mula sa mga produkto ng aming mga customer, kaya't talagang pumasok sila sa merkado tulad ng pinlano."

Sinabi ng isang executive ng TSMC sa kaganapan, "Sinimulan ng N3E ang paggawa ng masa tulad ng pinlano sa ika -apat na quarter ng nakaraang taon. Nakita namin ang mahusay na pagganap ng produksyon mula sa mga produkto ng aming mga customer, kaya't talagang pumasok sila sa merkado tulad ng pinlano."

Ang pangunahing detalye ng proseso ng N3E ay ang pagpapagaan nito kumpara sa unang proseso ng N3 ng TSMC (na kilala rin bilang N3B).Sa pamamagitan ng pag -alis ng ilang mga layer na nangangailangan ng EUV lithography at ganap na maiwasan ang paggamit ng double patterning ng EUV, binabawasan ng N3E ang mga gastos sa produksyon, pinalawak ang window ng proseso, at nagpapabuti ng ani.Gayunpaman, ang mga pagbabagong ito kung minsan ay binabawasan ang density ng transistor at kahusayan ng kuryente, isang trade-off na maaaring mapawi sa pamamagitan ng pag-optimize ng disenyo.

Sa unahan, ang proseso ng N3P ay nagbibigay ng optical scaling para sa N3E at nagpapakita rin ng promising na pag -unlad.Naipasa nito ang kinakailangang sertipikasyon ng kwalipikasyon at nagpapakita ng pagganap ng ani na malapit sa N3E.Ang susunod na ebolusyon ng portfolio ng teknolohiya ng TSMC ay naglalayong mapabuti ang pagganap ng hanggang sa 4% o bawasan ang pagkonsumo ng kuryente sa pamamagitan ng halos 9% sa parehong bilis ng orasan, habang pinapataas din ang transistor density ng hybrid na disenyo ng pagsasaayos ng disenyo ng 4%.

Ang N3P ay nagpapanatili ng pagiging tugma sa mga module ng IP ng N3E, mga tool sa disenyo, at mga pamamaraan, ginagawa itong isang kaakit -akit na pagpipilian para sa mga nag -develop.Tinitiyak ng pagpapatuloy na ito na ang karamihan sa mga bagong disenyo ng chip (CHIP) ay inaasahan na lumipat mula sa paggamit ng N3E hanggang N3P, na ginagamit ang pinahusay na pagganap at kahusayan ng gastos sa huli.

Ang pangwakas na trabaho sa paghahanda ng produksyon para sa N3P ay inaasahang magaganap sa ikalawang kalahati ng taong ito, kung papasok ito sa yugto ng HVM (Mass Production).Inaasahan ng TSMC na agad na gamitin ito ng mga taga -disenyo ng chip.Dahil sa mga pakinabang ng pagganap at gastos, ang N3P ay inaasahang mapapaboran ng mga customer ng TSMC, kabilang ang Apple at AMD.

Bagaman ang eksaktong petsa ng paglulunsad ng N3P batay sa mga chips ay hindi pa rin sigurado, inaasahan na ang mga pangunahing tagagawa tulad ng Apple ay gagamitin ang teknolohiyang ito sa kanilang serye ng processor sa pamamagitan ng 2025, kasama ang SOC para sa mga smartphone, personal na computer, at tablet.

"Matagumpay din nating naihatid ang teknolohiya ng N3P," sabi ng mga executive ng TSMC."Ito ay napatunayan at ang pagganap ng ani nito ay malapit sa N3E. (Ang teknolohiya ng proseso) ay nakatanggap din ng mga wafer ng mga customer ng produkto at ang paggawa ay magsisimula sa ikalawang kalahati ng taong ito. Dahil sa N3P's (PPA Advantage), inaasahan namin ang karamihan saWafers sa N3 upang dumaloy patungo sa N3p. "

Sa unahan, ang proseso ng N3P ay nagbibigay ng optical scaling para sa N3E at nagpapakita rin ng promising na pag -unlad.Naipasa nito ang kinakailangang sertipikasyon ng kwalipikasyon at nagpapakita ng pagganap ng ani na malapit sa N3E.Ang susunod na ebolusyon ng portfolio ng teknolohiya ng TSMC ay naglalayong mapabuti ang pagganap ng hanggang sa 4% o bawasan ang pagkonsumo ng kuryente sa pamamagitan ng halos 9% sa parehong bilis ng orasan, habang pinapataas din ang transistor density ng hybrid na disenyo ng pagsasaayos ng disenyo ng 4%.

Ang N3P ay nagpapanatili ng pagiging tugma sa mga module ng IP ng N3E, mga tool sa disenyo, at mga pamamaraan, ginagawa itong isang kaakit -akit na pagpipilian para sa mga nag -develop.Tinitiyak ng pagpapatuloy na ito na ang karamihan sa mga bagong disenyo ng chip (CHIP) ay inaasahan na lumipat mula sa paggamit ng N3E hanggang N3P, na ginagamit ang pinahusay na pagganap at kahusayan ng gastos sa huli.

Ang pangwakas na trabaho sa paghahanda ng produksyon para sa N3P ay inaasahang magaganap sa ikalawang kalahati ng taong ito, kung papasok ito sa yugto ng HVM (Mass Production).Inaasahan ng TSMC na agad na gamitin ito ng mga taga -disenyo ng chip.Dahil sa mga pakinabang ng pagganap at gastos, ang N3P ay inaasahang mapapaboran ng mga customer ng TSMC, kabilang ang Apple at AMD.

Bagaman ang eksaktong petsa ng paglulunsad ng N3P batay sa mga chips ay hindi pa rin sigurado, inaasahan na ang mga pangunahing tagagawa tulad ng Apple ay gagamitin ang teknolohiyang ito sa kanilang serye ng processor sa pamamagitan ng 2025, kasama ang SOC para sa mga smartphone, personal na computer, at tablet.

"Matagumpay din nating naihatid ang teknolohiya ng N3P," sabi ng mga executive ng TSMC."Ito ay napatunayan at ang pagganap ng ani nito ay malapit sa N3E. (Ang teknolohiya ng proseso) ay nakatanggap din ng mga wafer ng mga customer ng produkto at ang paggawa ay magsisimula sa ikalawang kalahati ng taong ito. Dahil sa N3P's (PPA Advantage), inaasahan namin ang karamihan saWafers sa N3 upang dumaloy patungo sa N3p. "