Pag-unawa sa Kapangyarihan ng S-R Latch: Isang Gateway sa Modern Electronics

Ang mga Latches ay mga simpleng digital na aparato na nag -iimbak ng isang kaunting impormasyon at panatilihin ang halagang iyon hanggang sa makakuha ito ng mga bagong signal ng pag -input.Ginagamit ang mga ito sa mga digital system upang pansamantalang humawak ng binary data.Ang mga latches ay maaaring gawin gamit ang iba't ibang uri ng mga pangunahing gate ng lohika tulad ng at, o, hindi, NAND, at NOR GATES.Ang artikulong ito ay galugarin ang disenyo, pag-andar, pagkakaiba-iba, at paggamit ng S-R latch, na binibigyang diin ang pinakamahusay na papel nito sa mga modernong elektronika at ang paggamit nito sa mga praktikal na circuit at digital logic simulation.

Catalog

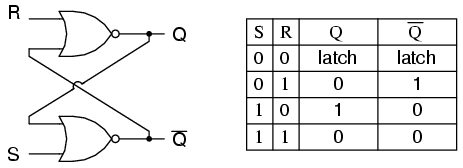

Larawan 1: S-R Latch Circuit Diagram

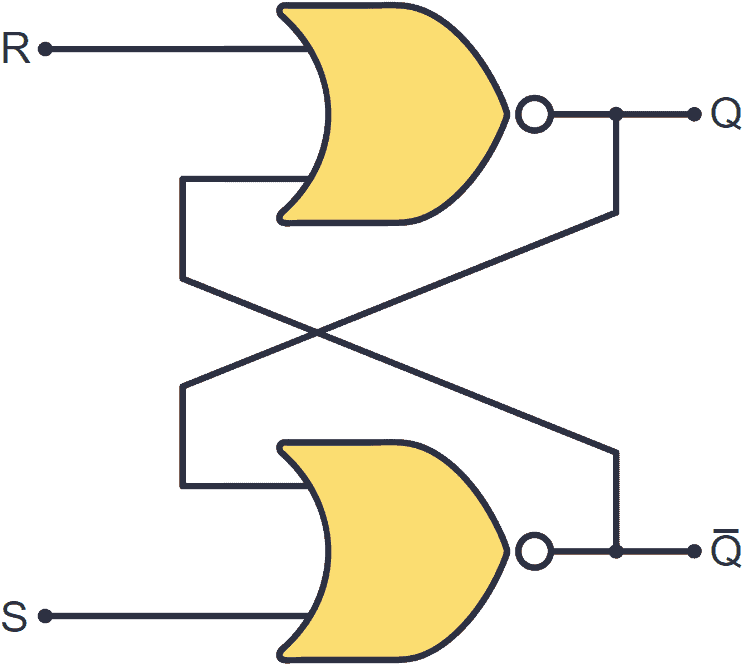

Istraktura ng S-R latch

Ang S-R (set-reset) latch, isang pundasyon sa digital electronics, ay isang bistable multivibrator.May kakayahang mapanatili ang isa sa dalawang magkakaibang, matatag na estado nang walang hanggan nang walang panlabas na pag -input.Ang pag -andar na ito ay nagbibigay ng SR latch ng isang pangunahing sangkap sa pag -iimbak ng memorya at paglipat ng mga operasyon sa iba't ibang mga elektronikong aparato.

Sa istruktura, ang SR latch ay binubuo ng dalawang magkakaugnay o mga pintuan na nakaayos sa isang disenyo ng feedback loop.Ang tiyak na pag -aayos ay mahalaga dahil nag -aalok ito ng mga kinakailangan para sa kakayahang umangkop.Ang bawat output ng Gate ay konektado nang direkta sa pag -input ng iba pa, na lumilikha ng isang tuluy -tuloy na loop ng puna na sumasailalim sa operasyon ng latch.

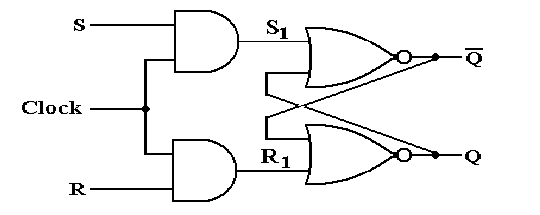

Larawan 2: S-R Latch at ang Clock Signal (CLK)

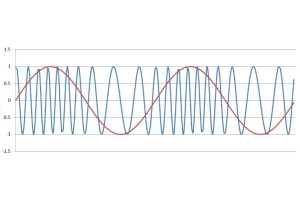

Ang pagpapalawak sa pangunahing disenyo, ang gated SR latch ay nagpapakilala ng isang karagdagang, input: ang signal ng orasan (CLK).Ang pagpapahusay na ito ay nagsasama ng isang pag -input ng orasan na nagdadala ng layer ng kontrol, pagsasama ng mga operasyon ng latch sa mga system na nangangailangan ng pag -synchronise.Ang pag -synchronize na ito ay obligado habang tinutukoy nito ang tumpak na mga sandali kapag ang latch ay maaaring magbago ng mga estado, naaangkop na inilarawan ng salitang "gated."Tinitiyak ng pagsasama ng signal ng orasan na ang mga pagbabago sa estado ng output ng latch ay nangyayari lamang sa panahon ng aktibong yugto ng orasan, karaniwang sa pagtaas o pagbagsak ng gilid ng signal ng CLK.

Ang pagpapakilala ng input ng CLK ay hindi lamang pinapanatili ang mga katangian ng pangunahing SR latch ngunit din nakahanay sa operasyon nito kasama ang temporal na dinamika ng mas malaking digital system.Ang pagnanais ng pagkakahanay na ito para sa pagpapanatili ng integridad ng data at tinitiyak na ang mga paglilipat ng estado ay nangyayari nang walang mga glitches o hindi sinasadyang mga pagbabago, lalo na sa mga kumplikadong pagsasaayos ng circuit kung saan maaaring makipag -ugnay ang maraming mga latch.Sa pamamagitan ng pagkontrol kapag ang latch ay tumugon sa mga set at pag-reset ng mga utos, maiiwasan ng system ang mga isyu tulad ng mga kondisyon ng lahi at iba pang mga error na may kaugnayan sa tiyempo na kung hindi man ay makagambala sa katatagan at pagganap ng system.

Mga estado ng pagpapatakbo ng S-R latch

Ang operasyon nito ay nakasalalay sa mga input ng dalawang signal signal: set (s) at i -reset (r).Dito, ipinapaliwanag namin kung paano nakakaapekto ang mga input na ito sa mga output at mga estado ng SR latch.

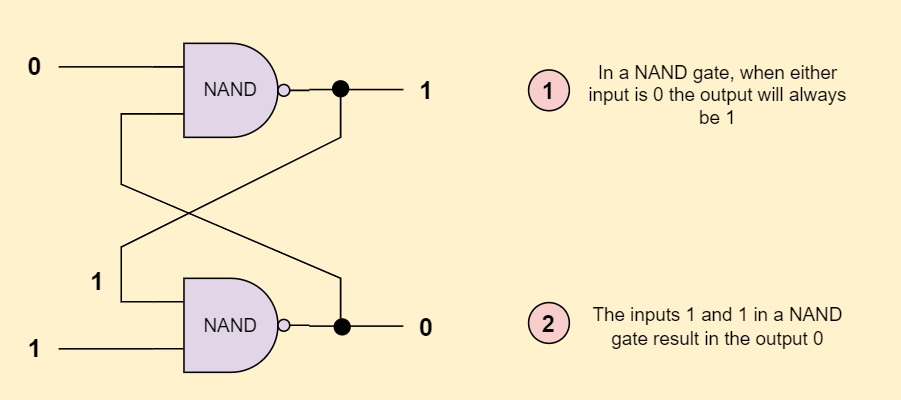

Kaso 1: Itakda ang kondisyon

Kapag ang set (s) input ay mataas (1) at ang pag -reset (r) input ay mababa (0), ang latch ay pumapasok sa nakatakdang kondisyon.Sa estado na ito, ang gate ng NAND na konektado sa R input ay mag-output ng isang mababang signal dahil sa mataas na input mula sa S. Ang mababang signal na ito ay nagiging sanhi ng pangalawang gate ng NAND na mag-output ng isang mataas na signal, na nagtatakda ng Q hanggang mataas (1) at Q-barsa mababa (0).Ang estado na ito ay matatag at panatilihin ang Q mataas hanggang sa magbago ang mga input, na ipinapakita ang kakayahan ng latch na mag -imbak ng isang mataas na estado.

Larawan 3: Ang itinakdang estado

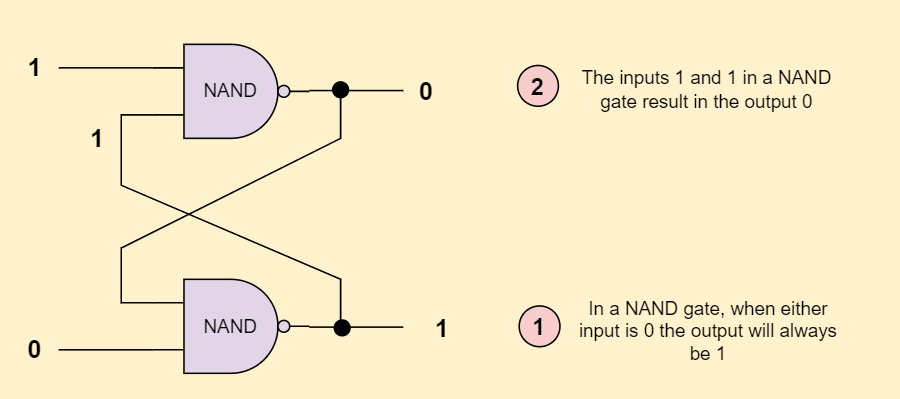

Kaso 2: Kondisyon ng pag -reset

Kapag ang S ay mababa (0) at R ay mataas (1), ang latch ay pumapasok sa kondisyon ng pag -reset.Dito, ang mataas na pag -input sa R at ang mababang pag -input sa S gawin ang NAND gate na konektado sa R output ng isang mababang signal.Ang mababang signal na ito ay nagtatakda ng Q hanggang Low (0) at Q-bar hanggang sa mataas (1), na epektibong i-reset ang latch.Ipinapakita nito ang kakayahan ng latch na bumalik sa isang matatag na mababang estado sa Q kapag binigyan ng tamang mga input.

Larawan 4: Ang estado ng pag -reset

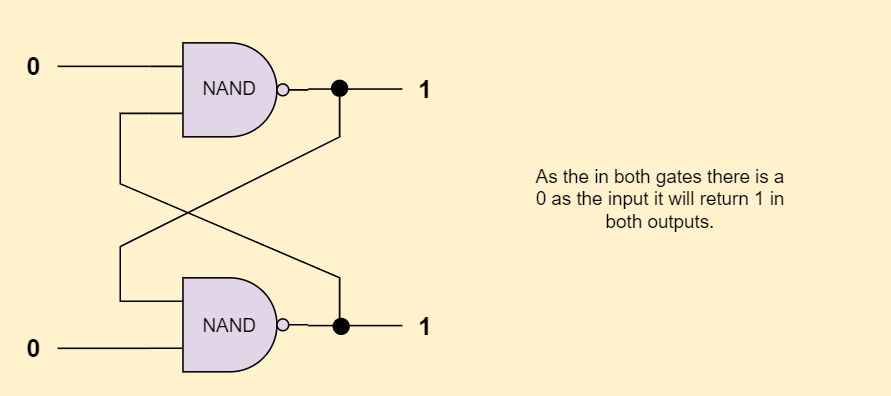

Kaso 3: Hindi wastong estado

Kung ang parehong S at R ay mababa (0), ang parehong mga input sa mga pintuang NAND ay mababa, na nagiging sanhi ng parehong mga output Q at Q-bar na mataas.Ang estado na ito ay tinatawag na hindi wasto o ipinagbabawal dahil sinisira nito ang pangunahing panuntunan na ang Q at Q-bar ay dapat palaging magkasalungat.Ang sitwasyong ito ay nagtatampok ng limitasyon ng SR latch, na binibigyang diin ang kahalagahan ng pag -iwas sa mga hindi matatag na estado sa pamamagitan ng wastong pamamahala ng pag -input.

Larawan 5: Ang hindi wastong estado

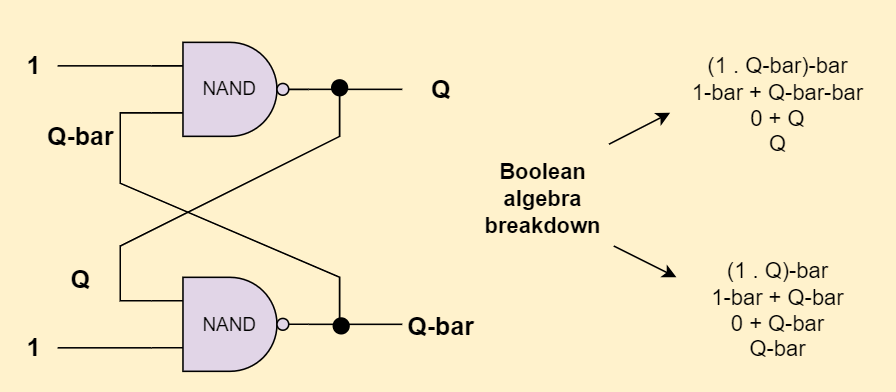

Kaso 4: Hold Condition

Kapag ang parehong mga input ay mataas (1), ang mga output ay nakasalalay sa nakaraang estado ng latch kaysa sa kasalukuyang mga input.Ito ay kilala bilang ang kondisyon ng hawak, kung saan ang Q at Q-bar ay nananatiling hindi nagbabago, na pinapanatili ang huling wastong estado ng latch.Para sa ilang mga aplikasyon, mahalaga na mapanatili ang latched na estado sa mahabang panahon nang walang pagbabago, tulad ng mga cell ng imbakan ng memorya kung saan ang integridad ng data ay may kahalagahan.

Larawan 6: Ang Estado ng Hold

S-r latch na may isang talahanayan ng katotohanan

Ang talahanayan na ito ay hindi lamang isang teoretikal na tool ngunit praktikal din ito para sa parehong mga taga -disenyo ng circuit at mag -aaral.Tinutulungan silang makita kung paano kumikilos ang latch sa ilalim ng maraming mga kondisyon.Sa ibaba, ipinakita namin ang komprehensibong talahanayan ng katotohanan para sa SR latch, na sinusundan ng mga paliwanag at praktikal na pananaw para sa bawat kondisyon.

|

S |

R |

Q |

Q-bar |

Estado |

|

0 |

0 |

1 |

1 |

Hindi wasto |

|

0 |

1 |

0 |

1 |

I -reset |

|

1 |

0 |

1 |

0 |

Itakda |

|

1 |

1 |

Q |

Q-bar |

Hawakan |

Tsart 1: sr

Latch Truth Table

Paliwanag ng bawat hilera

Itakda ang kondisyon (s = 1, r = 0): Ipinapakita ng hilera na ito na kapag ang S ay mataas at ang R ay mababa, ang Q ay nakatakda sa mataas (1) at q-bar hanggang mababa (0).Ito ay sumasalamin sa tugon ng circuit sa isang set na utos, na epektibong nag -iimbak ng isang '1'.

Reset Condition (s = 0, r = 1): Dito, ang mga input ay nagpapahiwatig ng isang operasyon ng pag -reset.Dahil dito, ang Q ay na-reset sa mababang (0) at ang Q-bar ay nakatakda sa mataas (1).Ipinapakita ng estado na ito ang kapasidad ng latch na bumalik sa isang '0'.

Hindi wastong kondisyon (s = 0, r = 0): Ang parehong mga output ay nagiging mataas sa kondisyong ito, na sa pangkalahatan ay maiiwasan dahil nagreresulta ito sa parehong mga output na magkapareho.Maaari itong humantong sa kawalang-tatag o hindi natukoy na pag-uugali sa latch, dahil nilalabag nito ang panuntunan na ang Q at Q-bar ay dapat palaging magkasalungat.

Hold Condition (s = 1, r = 1): Sa sitwasyong ito, pinapanatili ng latch ang nakaraang estado, na ipinapakita ang kakayahang hawakan ang huling itinakdang estado maliban kung malinaw na nag -utos na magbago.

Mga praktikal na pananaw at tip

Pag-unawa sa mga output: laging tandaan na ang Q at Q-bar ay may perpektong mga pandagdag.Ang anumang paglihis mula sa panuntunang ito (tulad ng nakikita sa hindi wastong kondisyon) ay nagpapahiwatig ng isang problema o maling pagsasaayos.

Pag -iwas sa hindi wastong estado: kinakailangan na mag -ingat ang mga taga -disenyo upang maiwasan ang sitwasyon kung saan ang S at R ay parehong mababa.Ang pagpapatupad ng karagdagang lohika o interlocks ay makakatulong upang maiwasan ang estado na ito.

Paggamit ng Hold Condition: Ang Hold Condition ay maaaring maging maginhawa sa mga aplikasyon na nangangailangan ng pangangalaga ng data sa paglipas ng panahon.Ang pagpapanatili ng integridad ng data ay maaaring depende sa pagtiyak na ang latch ay hindi sinasadyang pumasok sa set o i -reset ang estado.

Pagbibigay -kahulugan sa Talahanayan ng Katotohanan: Kapag nagdidisenyo o nag -debug ng mga circuit, sumangguni sa talahanayan ng katotohanan upang mahulaan kung paano makakaapekto ang mga pagbabago sa input sa output, lalo na sa mga kumplikadong circuit kung saan ginagamit ang maraming mga latch.

Functional dynamics ng S-R latch

Ang latch ng S-R (set-reset) ay gumagana nang maayos kung ang mga input nito ay pinamamahalaan nang tama.Upang maunawaan kung paano ito gumagana, kailangan mong malaman kung paano nakakaapekto ang iba't ibang mga kumbinasyon ng input sa mga output, Q at Q-bar (ang kabaligtaran ng Q).

Larawan 7: S-R latch

Kung ang parehong mga set (s) at pag-reset (r) ay isinaaktibo nang sabay (s = 1 at r = 1), ang latch ay pumapasok sa isang "ipinagbabawal na estado," kung saan ang parehong mga output, q at q-bar, ay 0.Ito ay isang problema sapagkat normal, ang Q at Q-bar ay dapat na magkasalungat.

Sa ilalim ng normal na mga kondisyon, upang itakda ang latch, isinaaktibo mo ang S (itakda ang S hanggang 1) at i -deactivate ang R (itakda ang R hanggang 0).Ginagawa nitong mataas ang q (1) at q-bar na mababa (0), na nagpapakita ng latch ay maaaring mag-imbak ng isang 1. Upang i-reset ang latch, isinaaktibo mo ang R (itakda ang R hanggang 1) at i-deactivate ang S (itakda ang S hanggang 0).Ginagawa nitong mababa ang q (0) at Q-bar go high (1), na nagpapakita ng latch ay maaaring limasin ang sarili at mag-imbak ng 0.

Kapag ang parehong mga input ay na -deactivate (s = 0 at r = 0), pinapanatili ng latch ang huling estado nito, alinman sa set o i -reset.Ito ay mabuti para sa pag -iimbak ng data o pagpapanatili ng isang estado nang hindi nangangailangan ng patuloy na pag -input.

Ang mga kondisyon ng lahi ay maaaring kumplikado ang operasyon ng S-R latch.Ang mga pagkakamali na ito ay nangyayari kapag ang mga output ay lubos na umaasa sa tiyempo ng mga pagbabago sa pag -input, na humahantong sa hindi mahuhulaan na mga resulta kung nagbabago ang mga input sa halos parehong oras.Upang maiwasan ito at matiyak na ang mga latch ay gumagana nang maaasahan, ang mga mekanismo ng pag-aalis ng oras ay madalas na ginagamit.Ang mga pagkaantala na ito ay siguraduhin na ang isang input ay aktibo pagkatapos ng iba ay nagkaroon ng oras upang patatagin.Para sa latch na gagamitin sa mga digital circuit kung saan kinakailangan ang tumpak na tiyempo, dapat itong gumanap nang palagi at mapanatili ang mga matatag na output.Ginagawa ito sa pamamagitan ng kinokontrol na tiyempo.

Logic diagram ng S-R latch

Ang SR Latch ay isang pangunahing sunud -sunod na lohika circuit na may dalawang pangunahing pagsasaayos: Ni o NAND Gates.Ang bawat pag -setup ay nakakaapekto kung paano gumagana ang latch at tumugon sa mga input, na nagpapahintulot sa pagpapasadya para sa iba't ibang mga elektronikong aplikasyon.

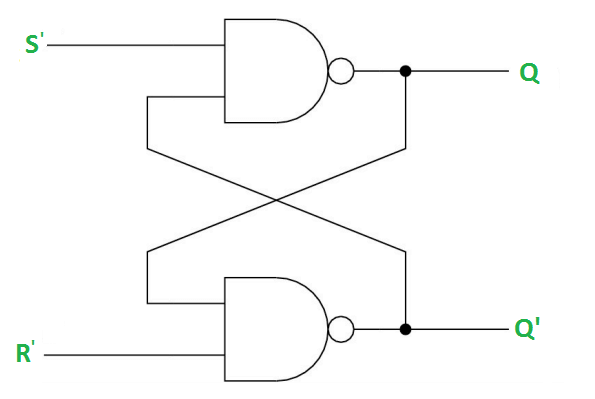

Larawan 8: Ang diagram ng Logic ay kumakatawan sa S-R latch gamit ang NAND Gate

Pagpapatupad gamit ang NAND Gates

Kapag nagtatayo ng isang SR latch na may mga pintuan ng NAND, ginagamit ang isang feedback loop upang mapanatili ang estado nito.Pinapayagan ng setup na ito ang latch na panatilihin ang nakaraang estado kapag ang parehong mga input (S at R) ay mababa.Ang NAND Gates Output ay mataas maliban kung ang parehong mga input ay mataas.Ang estado ng latch ay nagbabago kapag ang isang input ay mataas at ang isa ay mababa.Pinakamabuting iwasan ang pagtatakda ng parehong S at R mataas sa parehong oras dahil pinipilit nito ang parehong mga output na bumaba, na humahantong sa isang hindi natukoy na estado kung saan ang mga output ay hindi na pantulong.Ang wastong pamamahala ng pag-input ay isang kinakailangan upang maiwasan ang kawalang-tatag sa mga latch na batay sa NAND.

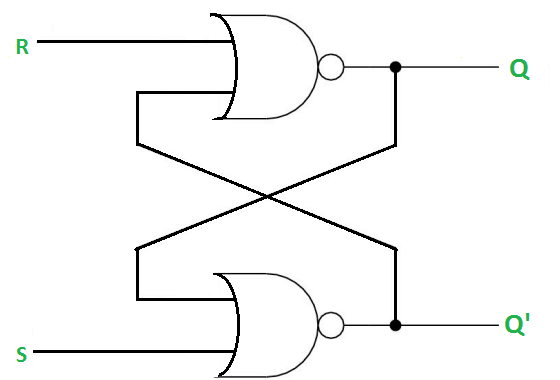

Pagpapatupad gamit ang mga pintuan

Ang paggamit ng mga pintuan para sa isang latch ng SR ay nagbabago sa mga kondisyon ng pagpapatakbo kumpara sa mga pintuan ng NAND.Sa pagsasaayos na ito, ang latch ay humahawak ng estado nito kapag ang parehong mga input ay mataas.Ang latch ay nagbabago ng estado kapag ang isang input ay mababa at ang isa ay mataas.Ni ang mga gate output ay mataas lamang kung ang parehong mga input ay mababa.Ang pag-setup na ito ay kapaki-pakinabang sa mga circuit kung saan ang default na estado ay magkaroon ng parehong mga output na mababa, tinitiyak ang mahuhulaan na output sa ilalim ng mga kondisyon ng high-input.Gayunpaman, pinakamahusay na maiwasan ang pagtatakda ng parehong mga input na mababa sa parehong oras, dahil ito ay nagiging sanhi ng magkasalungat na mga output at binabawasan ang pagiging maaasahan ng latch.

Larawan 9: Ang Logic Diagram ay kumakatawan sa S-R Latch gamit ang NOR GATE

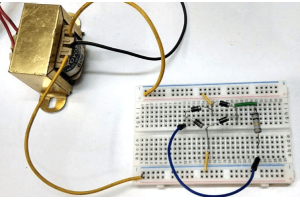

Halimbawa ng circuit

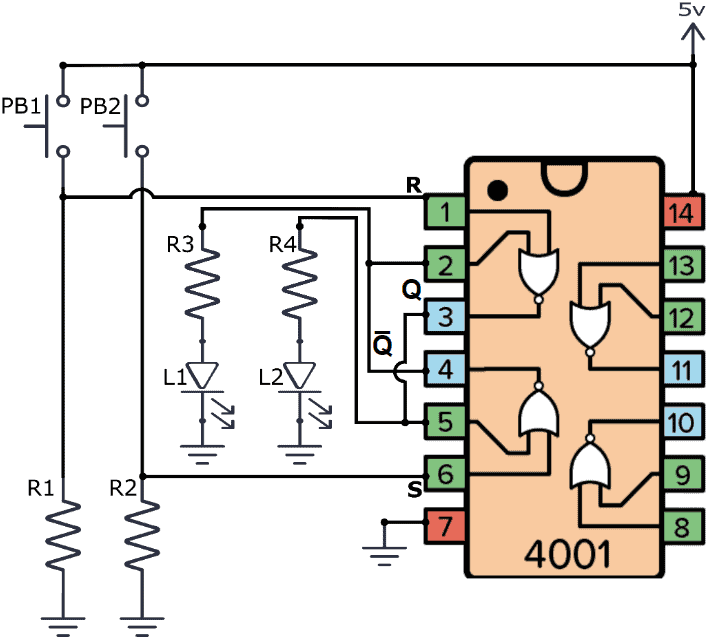

Ang paggalugad kung paano gumagana ang mga latch ng SR sa totoong buhay ay nagpapakita ng kanilang pagiging kapaki -pakinabang.Ang isang mabuting halimbawa ay isang circuit gamit ang CD4001 chip, na mayroong apat o mga pintuan.Ipinapakita ng circuit na ito kung paano makontrol ang mga latch ng SR tulad ng mga LED na may mga simpleng pagkilos tulad ng pagpindot sa mga pindutan.

Sa halimbawang ito, ang NOR Gates sa CD4001 chip ay naka -set up upang gumawa ng isang SR latch.Dalawang pintuan ang konektado sa isang feedback loop upang mapanatili ang estado ng latch.Ang mga pushbuttons ay idinagdag sa circuit bilang mga input para sa set at i -reset.Ang pagpindot sa isang pindutan ay nagbabago sa estado ng input, na nagbabago sa latch at estado ng LED.Halimbawa, ang pagpindot sa mga ilaw na pindutan ng ilaw ay nag -iilaw sa LED, at mananatili itong naiilawan kahit na matapos ang pindutan, na ipinapakita kung paano maaaring mapanatili ng latch ang isang estado.

Upang gawing mas mahusay ang circuit, mas maraming mga LED ang maaaring maidagdag upang ipakita ang estado ng output ng parehong Q at Q-bar.Ginagawang madali itong makita kung paano gumagana ang latch, na kung saan ay kapaki -pakinabang sa mga kapaligiran sa pag -aaral.

Larawan 10: S-R latch gamit ang CD4001 chip

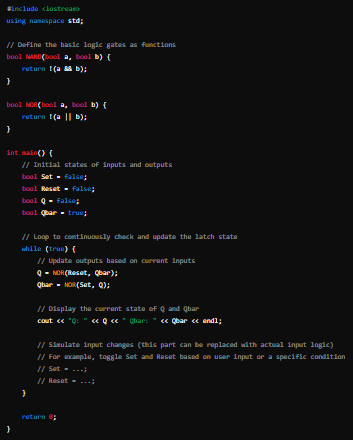

Pagpapatupad ng code

Ang pagsasalin ng pagpapatakbo ng lohika ng isang SR latch sa software ay nagpapakita kung paano maaaring gumana ang digital na disenyo ng lohika kapwa sa hardware at sa virtual simulation.Ang paggamit ng isang programming language tulad ng C ++ ay epektibo dahil sinusuportahan nito ang kumplikadong lohika at kontrol na kinakailangan upang gayahin ang mga pag -uugali ng hardware.

Upang makagawa ng isang SR latch sa C ++, magsisimula ka sa pamamagitan ng pagtukoy ng mga pangunahing logic gate bilang mga pag -andar na kumikilos tulad ng kanilang mga bersyon ng hardware.Halimbawa, ang isang function ng NAND gate ay ibabalik ang kabaligtaran ng at operasyon sa mga input nito.Katulad nito, ang isang pag -andar ng gate ay ibabalik ang kabaligtaran ng o operasyon.Sa mga pangunahing pag -andar na ito, maaari mong modelo ang pag -uugali ng SR Latch sa pamamagitan ng paglikha ng isang feedback loop sa pagitan ng mga pag -andar ng gate na ito, batay sa diagram ng circuit ng latch.

Ang code ay karaniwang may isang loop na patuloy na sinusuri ang mga estado ng mga input (set at i-reset) at ina-update ang mga output (Q at Q-bar) nang naaayon.Ang mga pahayag na kondisyon sa loob ng loop na ito ay matukoy kung paano nakakaapekto ang mga pagbabago sa pag -input ng mga output, malapit na tularan ang pisikal na pag -uugali ng SR Latch.Halimbawa, kung ang parehong set at pag -reset ng mga input ay mababa, ang mga output ay mananatiling pareho.Kung ang set ay mataas at ang pag-reset ay mababa, ang output q ay nagiging mataas at ang Q-bar ay nagiging mababa, ang pagtitiklop sa kondisyon ng set ng latch.

Narito ang isang simpleng halimbawa kung paano ito maaaring tumingin sa code:

Larawan 11: Sr Latch sa C ++

Ang code na ito ay nagtatakda ng isang simpleng SR latch gamit ang mga pintuan at patuloy na sinusuri at ina -update ang estado ng latch batay sa mga input.

Mga aplikasyon ng SR Latch

Mga control system sa mga operasyon ng motor: Ang SR latch na hinihiling ng mga system para sa kontrol ng motor.Gamit ang (mga) Start (stop (R) Pushbutton switch, ang SR latch ay nagpapanatili ng isang motor na tumatakbo kahit na matapos ang pindutan ng pagsisimula.Tinitiyak ng setup na ito ang patuloy na tumatakbo ang motor hanggang sa tumigil, pagpapahusay ng kaligtasan at kaginhawaan.

Pag -iimbak ng memorya at data: Kapag lumilikha ng mas malaking mga circuit ng memorya, ang SR latch ay gumaganap ng isang papel dahil maaari itong mag -imbak ng isang solong piraso ng data.Pinapanatili nito ang data sa isang matatag na estado hanggang sa na -update, na bumubuo ng batayan ng mga cell ng memorya sa digital computing.

Signal Control and Management: Sa control signal application, ang mga SR latches ay may hawak na mga tiyak na bits hanggang sa matugunan ang ilang mga kundisyon, tinitiyak ang wastong pagkakasunud -sunod at tiyempo sa mga operasyon.Ang katumpakan sa pagproseso ng signal at daloy ng data ay nakasalalay dito.

Debouncing Circuits: Ang mga latch ng SR ay nagpapatatag ng mga signal mula sa mga mekanikal na switch at pindutan, na pumipigil sa maling pag -trigger at mga pagkakamali na dulot ng "bounce" kapag pinindot ang mga switch.Ito ay partikular na akma sa mga digital na interface tulad ng mga keyboard.

Mga elemento ng pundasyon sa mga digital na sistema: Ang disenyo ng mga flip-flops at counter, na angkop para sa tiyempo at pagkakasunud-sunod sa mga elektroniko, ay lubos na nakasalalay sa mga latch ng SR.Ginagamit din sila bilang mga pulso latches para sa mabilis na pag -toggling ng estado.

Mga Dalubhasang Aplikasyon: Sa mga asynchronous system, ang mga pagkakaiba -iba tulad ng D latch ay ginagamit para sa ligtas at maaasahang paglipat ng data.Sa magkasabay na mga sistema ng two-phase, binabawasan ng mga latch ng data ang bilang ng transit, pagpapabuti ng kahusayan at pagbabawas ng pagkaantala.

Mas malawak na mga implikasyon sa electronics: Ang mga latch ng SR ay malawakang ginagamit sa mga circuit ng gating gating, na naglalaro ng isang bahagi sa pag -iingat ng enerhiya sa loob ng mga elektronikong aparato.Pinamamahalaan nila ang mga estado ng kuryente sa isang detalyadong antas, na nag -aambag sa pangkalahatang kahusayan ng enerhiya ng mga digital system.

Konklusyon

Ang S-R latch ay nagpapakita ng kahalagahan ng mga simpleng istruktura ng lohika sa mga kumplikadong digital system.Sa pamamagitan ng pagtingin sa iba't ibang mga pag-setup nito at kung paano ito gumagana, nakikita namin na ang S-R latch ay nagpapanatili ng matatag na data at ginagawang mahusay at maaasahan ang mga system.Maaari itong gumana sa ilalim ng iba't ibang mga kondisyon, na ipinakita ng mga talahanayan ng katotohanan at mga diagram ng lohika, ginagawa itong madaling iakma para sa maraming mga gamit, mula sa kontrol ng motor hanggang sa mga pangunahing digital circuit tulad ng mga flip-flops at counter.Ang S-R latch ay angkop sa maraming mga praktikal na aplikasyon, tulad ng mga cell ng memorya sa mga computer at pag-deboun ng mga circuit sa mga digital na interface, pagpapahusay ng kahusayan at pagbabawas ng mga error sa mga elektronikong aparato.Sa mga mekanismo ng feedback at maingat na pamamahala ng signal ng pag-input, ang S-R latch ay mabuti para sa pagdidisenyo ng mas maaasahan at mahusay na mga digital system.Ang pag-aaral ng pag-andar nito sa pamamagitan ng mga simulation ng software ay tumutulong na ikonekta ang teoretikal na elektronika sa mga aplikasyon ng real-world, na ginagawang isang mahalagang paksa ang S-R latch para sa parehong bago at nakaranas ng mga elektronikong inhinyero.

Madalas na Itinanong [FAQ]

1. Ano ang layunin ng sr latch?

Ang SR latch ay ginagamit upang mag -imbak ng isang solong piraso ng data;Ito ay isang pangunahing anyo ng memorya sa mga digital circuit.Ang pangunahing pag -andar nito ay upang mapanatili ang estado ng kaunti hanggang sa mabago ito ng mga signal ng input.

2. Mataas ba o mababa ba o mababa ang SR Latch?

Ang SR latch ay karaniwang aktibo nang mataas, nangangahulugang tumutugon ito sa mataas na mga input (antas ng logic 1).Kapag ang mga input s (set) at r (reset) ay mataas, nag -trigger sila ng mga pagbabago sa output.

3. Ano ang kawalan ng isang latch ng SR?

Ang isang pangunahing disbentaha ng SR latch ay ang pagkamaramdamin nito sa isang hindi wastong kondisyon kung saan ang parehong mga set at pag -reset ng mga input ay mataas nang sabay -sabay.Ang sitwasyong ito ay humahantong sa isang hindi natukoy na output, na maaaring magresulta sa hindi maaasahan o hindi mahuhulaan na pag -uugali.

4. Ano ang mga patakaran para sa sr latch?

Kung ang S (set) ay mataas at ang R (reset) ay mababa, ang output Q ay nakatakda sa mataas.

Kung ang R ay mataas at ang S ay mababa, ang output q ay na -reset sa mababa.

Kung ang parehong S at R ay mababa, ang output ay nagpapanatili ng nakaraang estado.

Kung ang parehong S at R ay mataas, ang output ay hindi natukoy o hindi wasto.

5. Ano ang memorya sa sr latch?

Ang memorya sa isang SR latch ay tumutukoy sa kakayahang mapanatili ang estado ng output (mataas o mababa) nang walang hanggan, hanggang sa makatanggap ito ng input upang baguhin ang estado.Ginagawa nitong isang bistable na aparato, mainam para sa simpleng pag -iimbak ng memorya.

6. Ano ang mga output ng SR latch?

Ang SR latch ay may dalawang output, q at q '(q-bar).Ang Q ay kumakatawan sa kasalukuyang estado, habang ang Q 'ay kabaligtaran ng Q. Kapag ang Q ay mataas, ang Q' ay mababa, at kabaligtaran.

7. Saan natin ginagamit ang Latch?

Kapag kinakailangan ang panandaliang pag-iimbak ng data o pagpapanatili ng estado, ang mga latch ay nagtatrabaho sa iba't ibang uri ng mga aplikasyon.Kasama dito ang pag-iimbak ng data sa mga flip-flops, rehistro, at mga yunit ng memorya, pati na rin sa mga system na nangangailangan ng pag-synchronize ng data at mga function ng hawak ng circuit.

Tungkol sa atin

ALLELCO LIMITED

Magbasa nang higit pa

Mabilis na pagtatanong

Mangyaring magpadala ng isang pagtatanong, tutugon kami kaagad.

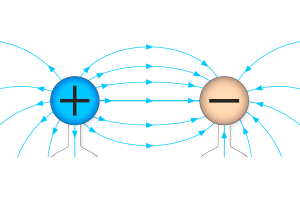

Static na kuryente

sa 2024/06/19

Ang gulugod ng mga sistemang elektrikal: isang komprehensibong gabay sa mga rectifier

sa 2024/06/17

Mga sikat na post

-

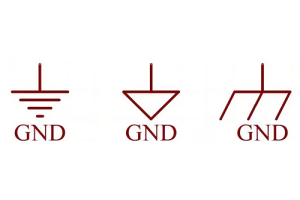

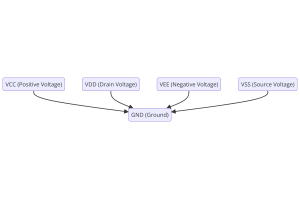

Ano ang GND sa circuit?

sa 1970/01/1 2946

-

RJ-45 Gabay sa Konektor: RJ-45 Mga Kulay ng Kulay ng Konektor, Mga Scheme ng Wiring, R-J45 Application, RJ-45 Datasheets

sa 1970/01/1 2502

-

Mga Uri ng Connector ng Fiber: SC vs LC at LC vs MTP

sa 1970/01/1 2091

-

Pag -unawa sa mga boltahe ng supply ng kuryente sa electronics VCC, VDD, VEE, VSS, at GND

sa 0400/11/9 1898

-

Paghahambing sa pagitan ng DB9 at RS232

sa 1970/01/1 1765

-

Ano ang baterya ng LR44?

Ang kuryente, na nasa buong lakas na iyon, tahimik na sumisid sa bawat aspeto ng ating pang-araw-araw na buhay, mula sa mga walang kabuluhan na mga gadget hanggang sa nagbabantang kagamitan sa medikal, gumaganap ito ng isang tahimik na papel.Gayunpaman, ang tunay na pagkakahawak ng enerhiya na ito, lalo na kung paano mag -imbak at mahusay na ma -output ito, ay hindi madaling gawain.Ito ay labag sa...sa 1970/01/1 1714

-

Pag -unawa sa mga batayan: paglaban sa inductance, atcapacitance

Sa masalimuot na sayaw ng elektrikal na engineering, isang trio ng mga pangunahing elemento ay tumatagal ng entablado: inductance, paglaban, at kapasidad.Ang bawat isa ay nagdadala ng mga natatanging katangian na nagdidikta sa mga dynamic na ritmo ng mga electronic circuit.Dito, nagsisimula kami sa isang paglalakbay upang matukoy ang mga kumplikado ng mga sangkap na ito, upang alisan ng takip ang ...sa 1970/01/1 1664

-

CR2430 Baterya Comprehensive Guide: Mga pagtutukoy, aplikasyon at paghahambing sa mga baterya ng CR2032

Ano ang baterya ng CR2430?Mga benepisyo ng mga baterya ng CR2430PamantayanCR2430 Mga Application ng BateryaKatumbas ng CR2430CR2430 kumpara sa CR2032Laki ng baterya CR2430Ano ang hahanapin kapag bumili ng CR2430 at katumbasData Sheet PDFMadalas na nagtanong Ang mga baterya ay ang puso ng maliit na elektronikong aparato.Kabilang sa maraming mga uri na magagamit, ang mga cell ng barya ay naglalaro n...sa 1970/01/1 1567

-

Ano ang RF at bakit natin ito ginagamit?

Ang teknolohiya ng Radio Frequency (RF) ay isang pangunahing bahagi ng modernong wireless na komunikasyon, na nagpapagana ng paghahatid ng data sa mga malalayong distansya nang walang pisikal na koneksyon.Ang artikulong ito ay sumasalamin sa mga pangunahing kaalaman ng RF, na nagpapaliwanag kung paano ginagawang posible ang electromagnetic radiation (EMR).Susuriin namin ang mga prinsipyo ng EMR, a...sa 1970/01/1 1550

-

CR2450 vs CR2032: Maaari bang magamit ang baterya?

Ang mga baterya ng Lithium Manganese ay may ilang pagkakapareho sa iba pang mga baterya ng lithium.Ang mataas na density ng enerhiya at mahabang buhay ng serbisyo ay ang mga katangian na mayroon sila sa karaniwan.Ang ganitong uri ng baterya ay nanalo ng tiwala at pabor sa maraming mga mamimili dahil sa natatanging kaligtasan nito.Mga mamahaling tech gadget?Mga maliliit na kagamitan sa aming mga ta...sa 1970/01/1 1519