Mastering SR Latches: Mga Simbolo, Pag -andar, at Praktikal na Aplikasyon

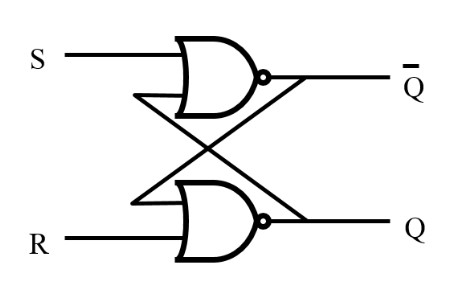

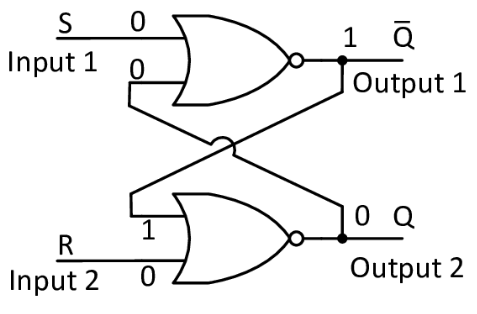

Ang isang SR latch ay isang asynchronous circuit na nagpapatakbo nang nakapag -iisa ng mga signal ng orasan, ginagawa itong isang maraming nalalaman tool sa iba't ibang mga aplikasyon.Nagpapanatili ito ng isang binary state - alinman sa mataas (1) o mababa (0) - at maaaring mag -imbak ng isang maliit na impormasyon, na hawak nito hanggang sa ang mga bagong signal ng pag -input ay nagdidikta ng pagbabago.Ang pangunahing elemento ng pag-iimbak ng binary ay itinayo gamit ang dalawang mga cross-coupled logic gate, karaniwang o o mga gate ng NAND.Ang mga set (s) ay nag -activate ng latch, ang pagtatakda ng output (q) hanggang sa mataas, habang ang pag -reset ng input (r) ay nagtatakda ng output sa mababa.Gayunpaman, ang sabay -sabay na mataas na signal sa parehong mga input ay humantong sa isang hindi natukoy na estado, dapat iwasan ng isang taga -disenyo ng kondisyon.Ang mga latch ng SR ay hindi lamang mga teoretikal na konstruksyon;Ang mga ito ay ipinatupad sa mga praktikal na sistema upang hawakan ang pansamantalang data, suportahan ang mga resulta ng pagproseso ng intermediate, at kahit na pamahalaan ang pagtuklas ng error sa mga kritikal na aplikasyon tulad ng aerospace at medikal na aparato, na nagpapakita ng kanilang kailangan sa disenyo ng digital circuit.Catalog

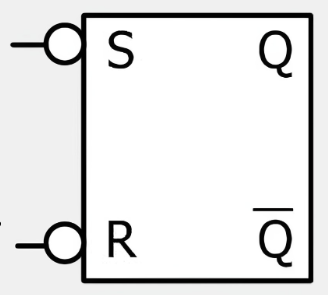

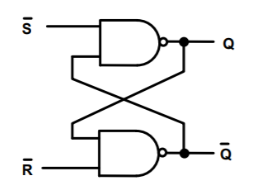

Larawan 1: Sr Latch

Ano ang isang sr latch?

Ang isang SR latch, o set-reset latch, ay isang pangunahing elemento ng imbakan ng binary na kabilang sa kategorya ng mga asynchronous circuit.Hindi tulad ng mga magkakasabay na circuit, ang mga latch ng SR ay nagpapatakbo nang walang signal ng orasan, na umaasa lamang sa direktang kontrol ng mga signal ng pag -input.Pinapayagan silang gumana nang nakapag -iisa sa loob ng mga digital na circuit.Ang isang latch ng SR ay maaaring mapanatili ang dalawang matatag na estado: Mataas (1) at Mababa (0), na nagpapagana upang mag -imbak ng isang solong impormasyon hanggang sa na -update ng mga bagong signal ng pag -input.

Ang pagtatayo ng isang SR latch ay karaniwang nagsasangkot ng dalawang cross-coupled logic gate, karaniwang o mga pintuan o mga pinturang NAND.Sa isang disenyo ng latch ng SR gamit ang NOR GATES, ang output ng bawat gate ay konektado sa input ng iba pa, na bumubuo ng isang feedback loop.Tinitiyak ng pagsasaayos na ito na ang latch ay maaaring mabilis na magbago ng mga estado batay sa mga signal ng pag -input habang pinapanatili ang katatagan hanggang sa isang bagong input ay nagtutulak ng pagbabago.

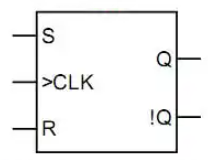

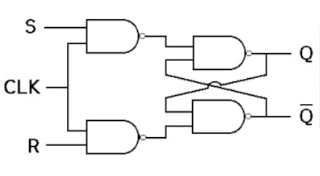

Larawan 2: SR Latch (2)

Itakda ang mga (mga) input: Kapag ang mga set input (s) ay isinaaktibo (mataas), ang latch output (Q) ay lumipat sa mataas (1).

I -reset ang Input (R): Kapag ang pag -reset ng input (r) ay isinaaktibo (mataas), ang output (q) ay lumipat sa mababang (0).

Ang parehong mga input ay mataas: Kung ang parehong mga input ng S at R ay mataas nang sabay -sabay, ang latch ay pumapasok sa isang hindi natukoy na estado, na dapat iwasan sa disenyo.

Ang mga latch ng SR ay mahalaga para sa pansamantalang pag -iimbak ng data at intermediate na resulta na may hawak sa mga digital system.Ang mga ito ay ang mga elemento ng pundasyon sa mas kumplikadong sunud-sunod na mga circuit tulad ng mga rehistro ng multi-bit shift, mga yunit ng memorya, at ilang mga uri ng mga counter.

Sa mga application na ito, ang mga latch ng SR ay nagbibigay ng matatag na pagpapanatili ng data at maaaring mabilis na tumugon sa mga pagbabago sa mga panlabas na signal, tinitiyak ang mahusay na operasyon ng buong elektronikong sistema.

Ang isa pang kritikal na aplikasyon ng mga latch ng SR ay sa error sa pagtuklas at lohika ng pagwawasto sa loob ng mga digital na circuit.Dahil sa kanilang kakayahang humawak ng isang matatag na estado, maaari nilang subaybayan ang mga pagbabago sa katayuan ng system at mabilis na bumalik sa isang paunang natukoy na ligtas na estado sa pagtuklas ng isang anomalya.Ang tampok na ito ay partikular na mahalaga sa mga sistema ng mataas na mapagkakatiwalaan tulad ng aerospace at medikal na aparato.

Simbolo ng latch ng SR

Ang pag -unawa sa simbolo at istraktura nito ay pangunahing upang maunawaan ang operasyon at praktikal na paggamit nito.Sa mga diagram ng circuit, ang SR latch ay karaniwang may dalawang pangunahing input port na may label na S (set) at R (RESET).Kinokontrol ng mga input na ito ang estado ng output ng latch, na karaniwang kinakatawan bilang Q. Ang ilang mga disenyo ay nagtatampok din ng kabaligtaran na output, na may label na Q ', na nagbibigay ng kabaligtaran na estado ng Q.

Larawan 3: Simbolo ng latch ng SR

Ang isang latch ng SR ay madalas na kinakatawan ng isang hugis -parihaba na simbolo na may mga input s at r at isang output Q. Sa ilang mga kaso, ipinapakita rin ang output q '.Ang malinaw na pag -label na ito ay nagbibigay -daan sa mga taga -disenyo ng circuit na mabilis na makilala ang pag -andar ng sangkap at ang papel nito sa loob ng mas malaking circuit.

Ang isang karaniwang variant ng SR latch ay may kasamang input ng orasan (CLK).Tinitiyak ng input ng CLK na ang mga pagbabago sa estado ay nagaganap sa pag -sync sa signal ng orasan, na nagpapagana ng tumpak na kontrol sa tiyempo.Sa pag -setup na ito, kahit na ang S o R ay isinaaktibo, ang estado ng latch ay nag -update lamang kapag ang signal ng CLK ay nakakatugon sa mga tiyak na kondisyon, karaniwang sa pagtaas o pagbagsak ng gilid.Pinipigilan nito ang mga error na dulot ng mga glitch ng signal ng input o hindi sinasadyang mga pagbabago.

Larawan 4: Simbolo ng latch na may orasan na SR

Ang na -clocked na simbolo ng SR Latch ay may kasamang mga input ng S, R, at CLK sa loob ng isang rektanggulo.Ang pamantayang representasyon na ito ay tumutulong sa mga taga -disenyo na maunawaan ang pag -andar ng latch at mga kinakailangan sa tiyempo nito.Halimbawa, sa mataas na pagganap na computing o kumplikadong mga sistema ng paglilipat ng data, tinitiyak ng maingat na kontrol ng CLK ang data ay naka-imbak at inilipat nang tumpak sa bawat yugto ng pagproseso, na-optimize ang pangkalahatang pagganap ng system at pagiging maaasahan.

Ang tumpak na kontrol ng mga input ng latch ng SR ay mahalaga, lalo na sa pagdidisenyo ng memorya ng high-speed at malaking kapasidad o pansamantalang mga buffer ng data.Sa pamamagitan ng pagdidisenyo ng mga logic circuit upang pamahalaan ang pag -activate ng S at R, ang mga kumplikadong pag -andar tulad ng pag -load ng data, pag -clear, o pag -reset ng estado ay maaaring makamit.Tinitiyak ng tumpak na control ng signal ng CLK na ang lahat ng mga operasyon ng data ay sumusunod sa isang paunang natukoy na pagkakasunud -sunod ng tiyempo, makabuluhang pagpapahusay ng kahusayan ng system at kakayahan sa pagproseso ng data.

Ang isang malalim na pag -unawa sa simbolo at istraktura ng SR latch ay hindi lamang sa tamang disenyo ng circuit at pag -aayos kundi pati na rin sa pagpapatupad ng kumplikadong mga operasyon ng digital na lohika at pagpapabuti ng pagganap ng system.Ito ay lalong kritikal sa mga aplikasyon na nangangailangan ng mataas na pagiging maaasahan at tumpak na kontrol, tulad ng aerospace at medikal na aparato.

Mga uri ng mga latch at ang kanilang mga prinsipyo sa pagtatrabaho

Ang mga latch ay pangunahing mga sangkap sa elektronikong disenyo, na nag -aalok ng magkakaibang mga pag -andar at malawak na aplikasyon.Ang mga pangunahing uri ng mga latch ay mga latch ng SR at D latches, bawat isa ay may natatanging operasyon at gumagamit ng mga kaso.

Sr latch

Ang SR latch, o set-reset latch, ay isang pangunahing aparato ng imbakan na kinokontrol ng dalawang input nito, s (set) at R (reset).

Kapag ang S input ay tumatanggap ng isang mataas na signal, ang output Q ay nagiging mataas, na nagpapahiwatig na nakatakda ang data.Kapag ang R input ay tumatanggap ng isang mataas na signal, ang output Q ay nagiging mababa, na nagpapahiwatig ng data ay na -reset.Kung ang parehong mga input ng S at R ay mataas nang sabay -sabay, ang latch ay pumapasok sa isang hindi natukoy na estado, na nagiging sanhi ng potensyal na kawalang -tatag ng output.Ang kondisyong ito ay dapat iwasan sa disenyo.Ang direktang tugon ng SR Latch sa mga signal ng pag -input ay ginagawang kapaki -pakinabang sa mga sitwasyon na nangangailangan ng mabilis na reaksyon.

D Latch

Ang d latch, na kilala rin bilang isang data latch o transparent latch, ay nag -aalok ng mas kumplikadong kontrol na may data input D at clock signal Clk.

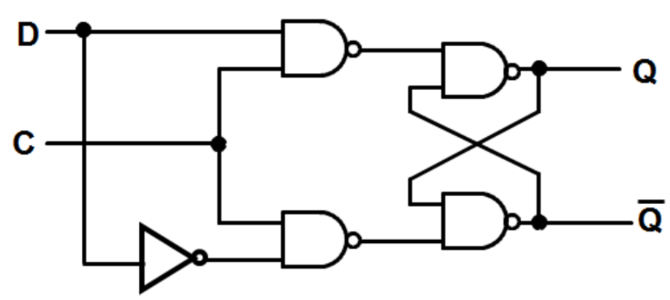

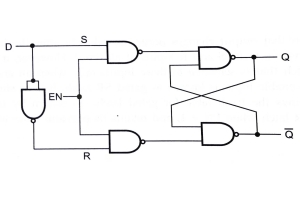

Larawan 5: D Latch

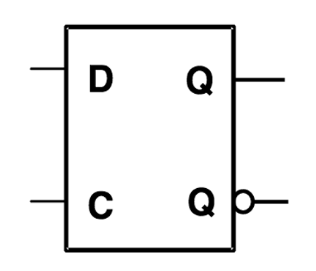

Larawan 6: D Simbolo ng Latch

Kapag ang CLK ay mataas, ang output Q ay sumusunod sa input D, na nagpapahintulot sa data na malayang dumaan sa latch.Kapag mababa ang CLK, ang kasalukuyang halaga ng D ay naka -lock, at ang output Q ay nananatiling pare -pareho hanggang sa susunod na mataas na signal ng CLK.Ang mekanismong ito ay ginagawang perpekto ang D latch para sa pansamantalang pag -iimbak ng data upang mai -synchronize ang iba't ibang mga bilis ng pagproseso sa loob ng isang system.

Ang mga latch ng SR at D ay may isang walang kaparis na papel sa pag -iimbak ng data at logic ng makina ng estado.Dahil sa kanilang direktang tugon sa antas ng pag -input, ang mga latch ay mahalaga sa pagdidisenyo ng mga asynchronous circuit.Nagbibigay ang mga ito ng mga mahahalagang pag -andar para sa mga kumplikadong paglilipat ng data at mga sistema ng pamamahala ng kuryente, na epektibong nag -iimbak ng impormasyon ng estado upang matiyak ang matatag na operasyon.Ang wastong paggamit ng mga latch na ito ay maaaring makabuluhang mapabuti ang pagiging maaasahan at kahusayan ng circuit, na ginagawa silang kailangang -kailangan sa mga modernong elektronikong sistema.

Talahanayan ng katotohanan ng isang latch ng SR

Larawan 7: Sr Nand Latch

|

S |

R |

Q |

Q ' |

Tandaan |

|

0 |

0 |

1 |

1 |

Ipinagbabawal |

|

0 |

1 |

1 |

0 |

ITAKDA |

|

1 |

0 |

0 |

1 |

I -reset |

|

1 |

1 |

Q |

Q ' |

Panatilihin |

Tsart 1: Talahanayan ng katotohanan ng sr latch gamit ang mga gate ng NAND

Larawan 8: SR o Latch

|

S |

R |

Q |

Q ' |

Tandaan |

|

0 |

0 |

Q |

Q ' |

Panatilihin |

|

0 |

1 |

1 |

0 |

I -reset |

|

1 |

0 |

0 |

1 |

ITAKDA |

|

1 |

1 |

0 |

0 |

Ipinagbabawal |

Tsart 2: Talahanayan ng katotohanan ng sr latch gamit ang mga pintuan

Ngayon kinukuha namin ang talahanayan ng katotohanan ng SR Latch gamit ang NOR GATE bilang isang halimbawa upang maunawaan ang kahulugan ng talahanayan ng katotohanan ng SR LATCH.

Mga estado ng input at output

Parehong S at R ay 0: Ang latch ay nananatili sa kasalukuyang estado nito.Ang output q ay mananatiling pareho, ito man ay 0 o 1.

Ang S ay 0 at R ay 1: Ang latch ay nag -reset, pinilit ang output q hanggang 0.

Ang S ay 1 at r ay 0: ang mga set ng latch, na ginagawa ang output q na katumbas ng 1.

Parehong S at R ay 1: Ang kundisyong ito ay hindi wasto o hindi natukoy, na madalas na tinutukoy bilang "ipinagbabawal" na estado sa isang latch ng SR.Sa kasong ito, ang q at q 'parehong pantay na 0, na humahantong sa isang hindi maliwanag na output.

Kapag ang S at R ay parehong 0, ang latch ay walang ginagawa at simpleng humahawak sa kasalukuyang halaga nito.Ito ay kapaki -pakinabang para sa pagpapanatili ng estado nang walang mga pagbabago.

Kapag ang S ay 0 at R ay 1, ang latch ay malinaw na sinabi na i -reset, siguraduhin na ang Q ay 0 anuman ang naunang estado nito.Ito ay isang tuwid na paraan upang malinis ang latch.

Kapag ang S ay 1 at r ay 0, ang latch ay nakatakda, tinitiyak ang Q ay nagiging 1. Ito ay kung paano ka nag -iimbak ng isang '1' sa latch.

Kapag ang S at R ay parehong 1, ang estado ay hindi pinapayagan sapagkat nagiging sanhi ito ng parehong mga output na 0, na magkakasalungat at hindi maaasahan.Dapat iwasan ng mga taga -disenyo ang kondisyong ito upang matiyak ang matatag na operasyon.

Mga kalamangan at kawalan ng mga latch

Ang mga latches ay malawakang ginagamit sa disenyo ng digital circuit dahil sa kanilang pagiging simple at mababang gastos.Ang mga katangiang ito ay nagbibigay-daan sa mga latches na gumana sa mataas na bilis na may mababang pagkonsumo ng kuryente, na ginagawang perpekto para sa mga high-speed digital system.Halimbawa, sa mga file ng rehistro ng processor, ang mga latch ay maaaring mabilis na mag -imbak at makuha ang data, makabuluhang pagpapalakas ng bilis ng pagproseso at kahusayan.

Mga kalamangan ng mga latch

Ang pagiging simple at pagiging epektibo sa gastos: Ang mga latch ay prangka na mga sangkap na mura upang maipatupad sa mga digital na circuit.

Mataas na bilis at mababang lakas: Pinapayagan ng kanilang disenyo para sa mabilis na operasyon na may kaunting pagkonsumo ng kuryente, na kritikal sa mga high-speed digital system.

Kahusayan sa Paghahawak ng Data: Sa mga application tulad ng mga file ng rehistro ng processor, ang mga latches ay nagbibigay ng mabilis na imbakan ng data at pagkuha, pagpapahusay ng pangkalahatang pagganap ng system.

Mga kawalan ng mga latch

Sa kabila ng kanilang mga pakinabang, ang mga latch ay may kilalang mga limitasyon sa ilang mga disenyo at aplikasyon.

Hindi mahuhulaan na pag -uugali sa mga asynchronous na disenyo: Kung walang control signal control, ang mga latches ay maaaring kumilos nang hindi mapag -aalinlangan.Sa mga latch ng SR, kung ang parehong mga set (s) at pag -reset (R) na mga input ay mataas nang sabay -sabay, ang output ay hindi natukoy, na humahantong sa kawalang -tatag.Ito ay may problema sa real-time control o safety-kritikal na mga aplikasyon, kung saan ang maaasahang output ay mahalaga.

Kumplikadong disenyo ng tiyempo: Ang pagdidisenyo ng mga latches ay nangangailangan ng maingat na mga pagsasaalang -alang sa tiyempo.Ang mga inhinyero ay dapat account para sa mga pagkaantala sa pagpapalaganap ng signal at mga kondisyon ng lahi upang maiwasan ang mga error sa tiyempo.Ang hindi maayos na disenyo ay maaaring magresulta sa mga pagbabago ng data bago nagpapatatag ang signal ng orasan, na nagiging sanhi ng katiwalian ng data o hindi tamang pagkuha ng data.Kinakailangan nito ang isang malalim na pag -unawa sa pagtatasa ng tiyempo at pag -uugali ng circuit.

Upang matugunan ang mga hamong ito, maaaring magamit ang mga tiyak na diskarte sa disenyo at mga diskarte:

Mga mekanismo ng pag -synchronize: Ang pagdaragdag ng mga mekanismo ng pag -synchronize ay makakatulong na pamahalaan ang mga asynchronous input at mabawasan ang hindi mahuhulaan na pag -uugali.

Pasadyang Pamamahala ng Orasan: Ang pagpapatupad ng mga na -customize na mga diskarte sa pamamahala ng orasan ay maaaring matiyak na ang data ay latched nang tama at sa tamang oras.

Ang paggamit ng mga tool ng EDA: Ang mga tool sa Modern Electronic Design Automation (EDA) ay nag -aalok ng mga advanced na pagsusuri at mga kakayahan sa pag -optimize.Ang mga tool na ito ay tumutulong sa paghula at paglutas ng mga isyu sa tiyempo at pag -synchronise sa yugto ng disenyo, pagpapabuti ng pagiging maaasahan at pagganap ng mga digital system gamit ang mga latch.Tinutulungan nila ang mga taga -disenyo sa pagkilala ng mga potensyal na problema nang maaga, tinitiyak na ang pangwakas na produkto ay nagpapatakbo ng maaasahan sa ilalim ng iba't ibang mga kondisyon.

Mga praktikal na aplikasyon ng mga latch ng SR

Ang mga latch ng SR, na kilala sa kanilang kakayahang mabilis at maaasahan na mapanatili ang estado, ay malawakang ginagamit sa iba't ibang mga elektronikong sistema.Nag -excel sila sa mga senaryo na nangangailangan ng pansamantalang pag -iimbak ng data o pagpapanatili ng estado.

Pansamantalang imbakan ng data

Ang mga latch ng SR ay madalas na ginagamit sa memorya ng cache upang pansamantalang mag -imbak ng data.Pinapayagan nito ang system na mabilis na ma-access ang madalas na ginamit na data, makabuluhang pagpapalakas ng mga kakayahan sa pagproseso ng data at kahusayan ng mga malalaking processors.

Mga file ng rehistro ng imbakan

Sa mga processors, pinapagana ng mga latch ng SR ang mabilis na pag -iimbak at pagkuha ng data sa mga file ng rehistro, pagpapahusay ng bilis ng pagproseso at pangkalahatang pagganap ng system.

Pagpapanatili ng mga signal ng kontrol

Sa mga digital control system, ang mga latch ng SR ay kapaki -pakinabang sa pagpapanatili ng estado ng ilang mga signal ng kontrol hanggang sa mga panlabas na kondisyon o lohika ng system ay nagdidikta ng isang pagbabago.Gayundin, tumutulong sila sa pagpapanatili ng mga estado sa loob ng system, tinitiyak ang pare -pareho na pagganap sa mga operasyon na nangangailangan ng katumpakan at pagiging maaasahan.

Trigger at counter circuit

Ang SR latch-based flip-flops ay karaniwang ginagamit sa mga circuit na nangangailangan ng naka-synchronize na operasyon, tulad ng mga digital na orasan at timer.Kinokontrol nila ang bilang ng mga pulso, tinitiyak ang tumpak na pag -timeke at maaasahang pagganap.Ang mga circuit na ito ay umaasa sa mga latch ng SR upang mapanatili ang tumpak na mga bilang, na nagpapadali sa tiyempo at pagkakasunud -sunod sa mga digital system.

Mga Pakikipag -ugnay sa Mekanikal

Ang mga latch ng SR ay epektibo sa pagtanggal ng mekanikal na bounce sa mga switch.Ang isang mekanikal na bounce ay nangyayari kapag ang isang switch ay bumubuo ng mabilis, paulit -ulit na pagbabago ng signal dahil sa hindi magandang pakikipag -ugnay.Ang mga latch ng SR ay nagpapatatag ng signal ng output, na pumipigil sa mga pagkakamali na dulot ng maingay na mga signal.

SR Flip-Flop

Ang isang SR flip-flop, na madalas na tinatawag na isang gilid-triggered set-reset flip-flop, ay binubuo ng dalawang magkakaugnay na mga latch ng SR.Ang istraktura ng dual-latch na ito ay nagbibigay-daan upang tumugon sa mga tiyak na mga gilid ng signal ng orasan (alinman sa pagtaas o pagbagsak) upang baguhin ang estado nito.Nakamit ito sa pamamagitan ng espesyal na kontrol ng lohika sa pagitan ng mga latch.Ang output ng unang latch ay nagiging bahagi ng input para sa pangalawang latch, at ang output ng pangalawang latch, naman, ay nakakaimpluwensya sa unang latch, na lumilikha ng isang interlocking feedback loop.

Larawan 7: SR flip-flop

Ang SR flip-flop ay nagbabago ng estado nang tumpak sa pagtaas ng signal o pagbagsak ng signal ng orasan.Ang interlocking feedback sa pagitan ng dalawang SR latches ay nagsisiguro na ang flip-flop ay nagbabago lamang ng estado bilang tugon sa gilid ng orasan, na nagbibigay ng matatag at maaasahang output.

Sa mga microprocessors at digital signal processors, ang mga SR flip-flop ay ginagamit para sa pag-sampling ng data at imbakan.Kinukuha nila at nagpapatatag ng data sa tinukoy na mga gilid ng orasan, tinitiyak ang maaasahang kasunod na pagproseso at pagsusuri ng data.

Ang mekanismo ng pag-trigger ng gilid ay tumutulong na maiwasan ang mga kondisyon ng lahi, kung saan ang iba't ibang mga bahagi ng circuit ay maaaring magbago ng estado nang sabay-sabay nang walang pag-synchronize, na potensyal na nagreresulta sa hindi matatag o hindi tamang mga output.Ang mga flip-flop ng SR ay mahalaga sa pagpapatupad ng mga tiyak na lohika ng protocol ng komunikasyon, tulad ng pag-synchronize ng frame at pagtuklas ng error.Ang kanilang katatagan at mabilis na oras ng pagtugon ay makakatulong na mapanatili ang kalidad ng paghahatid ng data at pagiging maaasahan ng system.

Ipinagbabawal na estado sa mga latch ng SR at SR flip-flops

Kapag nagdidisenyo ng mga latch ng SR at SR flip-flops gamit ang NAND at NOR GATES, kailangan nating bigyang pansin ang pamamahala at pag-iwas sa mga inhibitadong estado.Ang isang ipinagbabawal na estado ay nangyayari kapag ang parehong mga set (s) at pag -reset (r) na mga input ay sabay -sabay na mataas (para sa mga gate ng NAND) o mababa (para sa mga pintuan).Ang kumbinasyon na ito ay humahantong sa isang hindi tiyak na estado ng output, dahil ang output ay nakasalalay sa nakaraang estado ng circuit, na ginagawang hindi mahuhulaan.

Ipinagbabawal na estado sa Nand Gate Sr Latches

Kapag ang parehong S at R ay mababa, ang parehong mga output ay mataas, na lumalabag sa pantulong na katangian ng output ng latch.Nagreresulta ito sa isang hindi tiyak na estado.

Ipinagbabawal na estado sa Nor Gate Sr Latches

Kapag ang parehong S at R ay mataas, ang parehong mga output ay mababa, na lumilikha din ng isang hindi tiyak na estado.Maaari itong humantong sa hindi mahuhulaan na pag -uugali sa circuit.

Mga praktikal na diskarte upang maiwasan ang mga ipinagbabawal na estado

Pagdaragdag ng control logic

Gumamit ng karagdagang mga gate ng lohika upang masubaybayan ang mga estado ng S at R. Kung ang parehong mga input ng takbo patungo sa isang ipinagbabawal na estado, awtomatikong ayusin ang isang input upang maiwasan ang hindi tiyak na estado.Tinitiyak nito na ang mga output ay mananatiling matatag at mahuhulaan.Magpatupad ng isang lohika gate na namamagitan kapag ang S at R ay parehong mataas (o mababa), pag -aayos ng isang input upang mapanatili ang isang wastong estado.

Simulation ng software at pagsubok sa hardware

Magsagawa ng masusing mga simulation ng software upang makilala ang mga potensyal na ipinagbabawal na estado sa ilalim ng iba't ibang mga kondisyon ng operating.Pinapayagan nito ang mga taga -disenyo na makita at iwasto ang mga lohikal na error bago ang pisikal na pagpapatupad.Magsagawa ng malawak na pagsubok sa hardware upang mapatunayan na ang circuit ay hawakan nang tama ang lahat ng mga kumbinasyon ng pag -input.Ang hakbang na ito ay tumutulong upang matiyak na ang latch o flip-flop ay nagpapatakbo ng maaasahan sa mga senaryo ng real-world.

Konklusyon

Ang kakayahang umangkop at pagiging maaasahan ng SR latches ay binibigyang diin ang kanilang kabuluhan sa disenyo ng digital circuit.Sa pamamagitan ng paggalugad ng nuanced na pag -uugali ng mga latch ng SR sa pamamagitan ng kanilang mga representasyon ng simbolo, mga talahanayan ng katotohanan, at praktikal na aplikasyon, nakakakuha tayo ng isang komprehensibong pag -unawa sa kanilang operasyon at kahalagahan.Sa kabila ng mga potensyal na pitfalls ng mga hindi natukoy na estado sa mga asynchronous na disenyo, ang madiskarteng pagpapatupad ng control logic at malawak na kunwa ay maaaring mabawasan ang mga panganib na ito.Ang mga tool ng Advanced Electronic Design Automation (EDA) ay higit na mapahusay ang pagiging maaasahan at pagganap ng mga circuit na nagsasama ng mga latch ng SR sa pamamagitan ng paghula at paglutas ng mga isyu sa tiyempo at pag -synchronise.Ginamit man sa pansamantalang pag -iimbak ng data, pagpapanatili ng signal ng control, o pagtuklas ng error, ang mga latch ng SR ay nagpapatunay na maging pundasyon sa paglikha ng matatag at mahusay na mga digital system.Ang kanilang papel sa mga operasyon ng memorya ng high-speed at kasabay na pagproseso ng data sa mga kumplikadong aplikasyon ay nagpapakita ng kanilang walang hanggang kaugnayan.Tulad ng pagsulong ng teknolohiya, ang mga prinsipyo na namamahala sa mga latch ng SR ay patuloy na nagpapaalam at nagbibigay ng inspirasyon sa mga makabagong ideya sa mga digital na elektronika, tinitiyak na ang mga sangkap na ito ay mananatiling mahalaga sa pagbuo ng sopistikado at maaasahang mga elektronikong aparato.

Madalas na Itinanong [FAQ]

1. Ano ang isang SR latch?

Ang isang SR latch, o set-reset latch, ay isang pangunahing elemento ng imbakan ng binary na ginagamit sa mga digital circuit.Ito ay isang asynchronous circuit, nangangahulugang nagpapatakbo ito nang walang signal ng orasan, na umaasa sa direktang kontrol ng mga input nito upang baguhin ang mga estado.

2. Ano ang pag -andar ng SR sa lohika?

Sa lohika, ang mga input ng SR (set-reset) ay kumokontrol sa estado ng latch.

3. Anong uri ng lohika gate ang ginagamit ng isang latch ng SR?

Ang isang latch ng SR ay karaniwang gumagamit ng alinman sa mga pintuan o mga gate ng NAND.Sa isang latch na batay sa gate na batay sa gate, ang output ng bawat isa o gate ay pinapakain pabalik sa input ng iba pa, na lumilikha ng isang matatag na feedback loop.Sa isang latch na nakabase sa NAND na gate, isang katulad na pagsasaayos ng feedback ay ginagamit, ngunit ang mga antas ng lohika ay baligtad kumpara sa latch na batay sa NOR GATE.Ang parehong mga pagsasaayos ay nakamit ang parehong pangunahing pag -andar ng pagpapanatili ng isang binary state batay sa set at pag -reset ng mga input.

4. Paano gumagana ang isang latch?

Gumagana ang isang latch sa pamamagitan ng paggamit ng feedback upang mapanatili ang estado ng output nito batay sa mga input na ibinigay.Sa isang SR latch, ang mga set (s) at pag -reset (R) input ay kumokontrol sa estado ng output (Q).Kapag ang set input ay isinaaktibo (mataas), ang output ay nakatakda sa mataas (1).Kapag ang pag -reset ng input ay isinaaktibo (mataas), ang output ay na -reset sa mababa (0).Ang feedback loop sa disenyo ng latch ay nagsisiguro na kapag naitatag ang isang estado ng output, nananatiling matatag ito hanggang sa mabago ito ng isang bagong signal ng pag -input.

5. Ano ang kawalan ng isang latch ng SR?

Ang pangunahing kawalan ng isang latch ng SR ay ang hindi natukoy na estado na nangyayari kapag ang parehong mga set (s) at pag -reset (R) na mga input ay mataas nang sabay -sabay.Ang kundisyong ito ay humahantong sa isang hindi tiyak na estado ng output, na maaaring maging sanhi ng kawalang -tatag at hindi mahuhulaan na pag -uugali sa mga digital na circuit.Ang estado na "ipinagbabawal" na ito ay dapat iwasan sa disenyo upang matiyak ang maaasahang operasyon.

SR Latch, Set-Reset Latch, Asynchronous Circuit, Binary Storage Element, Digital Circuits, o Gates, NAND Gates, Feedback Loop, High State, Low State, Undefined State, Clock Signal, Direct Control, Pansamantalang Data Storage, Intermediate Result Holding,Error Detection, Aerospace Application, Medical Device, Circuit Design, Clocked SR Latch, Input Signals, Symbol at Structure, High-Speed Memory, Data Buffers, Timing Control, Tumpak na Kontrol, Pagpapanatili ng Estado, Microprocessors, Digital Signal Processors, Data Sampling, DataPag-iimbak, Edge-Triggered, SR Flip-Flop, Interlocking Feedback, Mga Kondisyon ng Lahi, Logic ng Protocol ng Komunikasyon, Pag-synchronize ng Frame, Error Detection, Signal Glitches, Electronic Design Automation, EDA Tools, Pag-synchronize Mekanismo, Pamamahala ng Custom Clock, Mga Error sa Tiyempo, Pagpapalaganap ng Pagpapalaganap,Mga kondisyon ng lahi, kumplikadong paglilipat ng data, mga sistema ng pamamahala ng kuryente, mekanikal na bounce, praktikal na aplikasyon, digital control system, logic gate, software simulation, hardware testing, ipinagbabawal na estado, pagiging maaasahan ng latch.

Tungkol sa atin

ALLELCO LIMITED

Magbasa nang higit pa

Mabilis na pagtatanong

Mangyaring magpadala ng isang pagtatanong, tutugon kami kaagad.

Isang Gabay sa Mga Pangunahing Kaalaman ng D Flip -Flops - Mga Circuits, Mga Talahanayan ng Katotohanan, Mga Uri, Bentahe at Mga Limitasyon

sa 2024/05/17

Paghahambing na gabay sa pagsusuri ng rheostat at potentiometer

sa 2024/05/17

Mga sikat na post

-

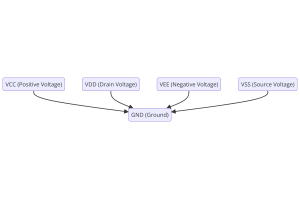

Ano ang GND sa circuit?

sa 1970/01/1 3274

-

RJ-45 Gabay sa Konektor: RJ-45 Mga Kulay ng Kulay ng Konektor, Mga Scheme ng Wiring, R-J45 Application, RJ-45 Datasheets

sa 1970/01/1 2817

-

Pag -unawa sa mga boltahe ng supply ng kuryente sa electronics VCC, VDD, VEE, VSS, at GND

sa 0400/11/20 2645

-

Mga Uri ng Connector ng Fiber: SC vs LC at LC vs MTP

sa 1970/01/1 2266

-

Paghahambing sa pagitan ng DB9 at RS232

sa 1970/01/1 1883

-

Ano ang baterya ng LR44?

Ang kuryente, na nasa buong lakas na iyon, tahimik na sumisid sa bawat aspeto ng ating pang-araw-araw na buhay, mula sa mga walang kabuluhan na mga gadget hanggang sa nagbabantang kagamitan sa medikal, gumaganap ito ng isang tahimik na papel.Gayunpaman, ang tunay na pagkakahawak ng enerhiya na ito, lalo na kung paano mag -imbak at mahusay na ma -output ito, ay hindi madaling gawain.Ito ay labag sa...sa 1970/01/1 1846

-

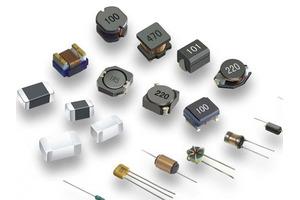

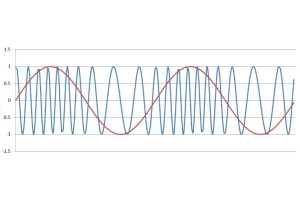

Pag -unawa sa mga batayan: paglaban sa inductance, atcapacitance

Sa masalimuot na sayaw ng elektrikal na engineering, isang trio ng mga pangunahing elemento ay tumatagal ng entablado: inductance, paglaban, at kapasidad.Ang bawat isa ay nagdadala ng mga natatanging katangian na nagdidikta sa mga dynamic na ritmo ng mga electronic circuit.Dito, nagsisimula kami sa isang paglalakbay upang matukoy ang mga kumplikado ng mga sangkap na ito, upang alisan ng takip ang ...sa 1970/01/1 1809

-

Ano ang RF at bakit natin ito ginagamit?

Ang teknolohiya ng Radio Frequency (RF) ay isang pangunahing bahagi ng modernong wireless na komunikasyon, na nagpapagana ng paghahatid ng data sa mga malalayong distansya nang walang pisikal na koneksyon.Ang artikulong ito ay sumasalamin sa mga pangunahing kaalaman ng RF, na nagpapaliwanag kung paano ginagawang posible ang electromagnetic radiation (EMR).Susuriin namin ang mga prinsipyo ng EMR, a...sa 1970/01/1 1801

-

CR2430 Baterya Comprehensive Guide: Mga pagtutukoy, aplikasyon at paghahambing sa mga baterya ng CR2032

Ano ang baterya ng CR2430?Mga benepisyo ng mga baterya ng CR2430PamantayanCR2430 Mga Application ng BateryaKatumbas ng CR2430CR2430 kumpara sa CR2032Laki ng baterya CR2430Ano ang hahanapin kapag bumili ng CR2430 at katumbasData Sheet PDFMadalas na nagtanong Ang mga baterya ay ang puso ng maliit na elektronikong aparato.Kabilang sa maraming mga uri na magagamit, ang mga cell ng barya ay naglalaro n...sa 1970/01/1 1800

-

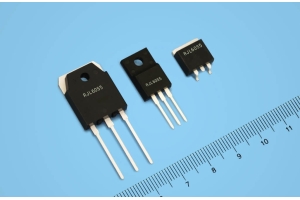

Komprehensibong gabay sa HFE sa mga transistor

Ang mga transistor ay mga mahahalagang sangkap sa mga modernong elektronikong aparato, pagpapagana ng pagpapalakas at kontrol ng signal.Ang artikulong ito ay sumasalamin sa kaalaman na nakapalibot sa HFE, kasama na kung paano pumili ng halaga ng HFE ng transistor, kung paano makahanap ng HFE, at ang pakinabang ng iba't ibang uri ng mga transistor.Sa pamamagitan ng aming paggalugad ng HFE, nakakaku...sa 5600/11/20 1782