Makabagong Gabay sa JK Flip-Flops: Pag-aaral ng Mga Talahanayan ng Katotohanan, Mekanismo, at Strategic Application

Ang artikulong ito ay galugarin ang arkitektura, operasyon, at magkakaibang mga aplikasyon ng JK flip-flop, na nagsisimula mula sa pangunahing istraktura at mga relasyon sa input-output, sa pamamagitan ng detalyadong mekanika ng pagpapatakbo, sa mga madiskarteng pagpapatupad nito sa mga kumplikadong digital system.Ang diskurso ay umaabot sa pagkilala sa pagitan ng mga variant na naka-trigger at antas na naka-trigger, na sinusuri ang kani-kanilang mga utility sa magkakasabay at hindi pangkaraniwang mga kapaligiran.Catalog

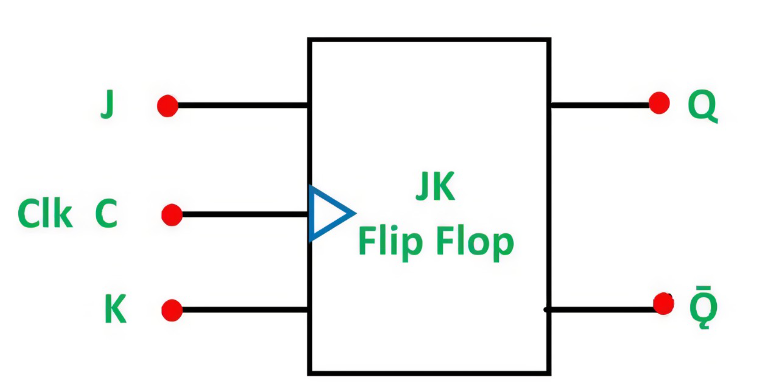

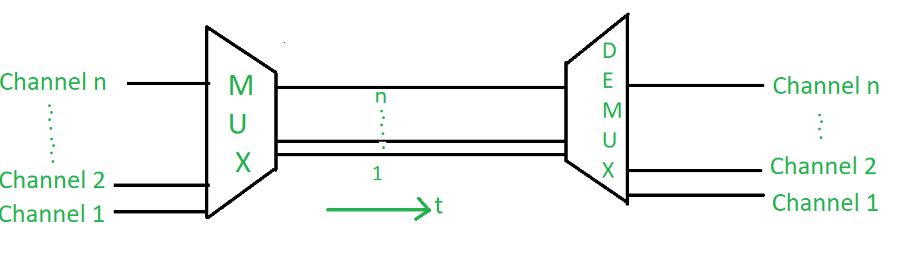

Larawan 1: JK flip-flop

Mga Pangunahing Kaalaman ng JK Flip-Flop

Ang JK Flip-Flop ay isang pangunahing sangkap sa Digital Electronics, na idinisenyo upang mag-imbak ng isang solong impormasyon.Nagtatayo ito sa mas simpleng SR flip-flop sa pamamagitan ng pagdaragdag ng puna, na tumutulong na maiwasan ang mga pagkakamali na kilala bilang "mga kondisyon ng lahi," kung saan ang output ay nagiging hindi matatag.

Ang flip-flop na ito ay may dalawang pangunahing input, j (set) at k (reset), at dalawang output: q at ang pandagdag nito, q '.Ang mga output na ito ay patuloy na sumasalamin sa kasalukuyang estado at kabaligtaran nito, na nagpapahintulot sa circuit na ayusin at tumugon sa mga pagbabago sa real-time na pag-input.

Ang JK flip-flop ay nagpapatakbo sa mga tiyak na paraan batay sa mga halaga ng input:

• Kapag ang parehong J at K ay 0: Ang flip-flop ay humahawak sa kasalukuyang estado nito.Walang mga pagbabago na nangyayari.

• Kapag ang parehong J at K ay 1: Ang flip-flop toggles ang estado nito.Kung ang Q ay 0, nagiging 1;Kung ang Q ay 1, lumipat ito sa 0. Ang pagkilos na ito ng toggle ay isang pangunahing tampok na nakikilala ang JK flip-flop mula sa mas simpleng mga disenyo.

• Kapag ang j ay 1 at k ay 0: Ang flip-flop ay nagtatakda ng estado nito, na ginagawang katumbas ng q.

• Kapag ang j ay 0 at k ay 1: Ang pag-reset ng flip-flop, na ginagawang katumbas ng q.

Ang pagpapatakbo ng JK flip-flop

Ang JK flip-flop ay gumaganap ng isang pangunahing papel sa mga digital na circuit sa pamamagitan ng pamamahala ng memorya at tiyempo sa pamamagitan ng isang coordinated na tugon sa mga signal ng pag-input at mga pulso ng orasan.Ang operasyon nito ay nakasalalay nang labis sa tiyempo ng mga input ng J at K na nauugnay sa signal ng orasan, na tumutukoy kung paano nagbabago ang output ng estado (Q at Q̅).Tinitiyak ng pag-synchronize na ang flip-flop ay kumikilos sa iba't ibang mga aplikasyon ng circuit.Ang flip-flop ay nakasalalay sa NAND o NOR GATES upang pamahalaan ang mga pagbabagong ito ng estado.

Hawak ang kasalukuyang estado- Kapag ang parehong mga input ng J at K ay mababa (0), pinapanatili ng flip-flop ang kasalukuyang estado nito.Ang mga logic gate na epektibong "i -lock" ang mga output, tinitiyak ang nakaraang estado (alinman sa mataas o mababa) ay pinananatili.Ang hawak na pag -andar na ito ay seryoso sa mga aplikasyon kung saan ang data ay dapat manatiling matatag hanggang sa isang tiyak na pagbabago ay dapat.

Pagtatakda ng Mataas na Output (Itakda ang Estado) -Kapag naganap ang tibok ng orasan at ang J ay mataas (1) habang ang k ay nananatiling mababa (0), ang mga logic gate ay nag-aayos upang itakda ang flip-flop.Nagdadala ito ng output Q sa isang mataas na estado (1).Ito ay kapaki -pakinabang sa mga sitwasyon kung saan ang circuit ay kailangang mag -trigger ng isang mataas na output, halimbawa, pag -activate ng isang aparato o pag -iimbak ng isang "1" sa memorya.

Pag -clear ng Output Mababa (Reset State) - Kung ang J ay mababa (0) at K ay mataas (1) sa oras ng isang tibok ng orasan, ang mga flip-flop na paglilipat sa isang estado ng pag-reset, na pinilit ang Q na bumaba (0).Ang pag -reset ng aksyon na ito ay madalas na ginagamit sa mga circuit na nangangailangan ng isang default o na -clear na estado pagkatapos makumpleto ang isang operasyon, tulad ng pag -clear ng data mula sa memorya.

Pag -toggling ng output - Ang natatanging tampok ng flip-flop ay lumitaw kapag ang parehong J at K ay mataas (1).Pagdating ng tibok ng orasan, ang flip-flop toggles, paglipat ng output mula sa kasalukuyang estado hanggang sa kabaligtaran.Kung ang Q ay mataas, ito ay nagiging mababa, at kung ang Q ay mababa, ito ay nagiging mataas.Ang pag -andar ng toggle na ito ay iginiit sa mga application tulad ng mga counter o aparato na kailangang alternate sa pagitan ng mga estado nang awtomatiko.

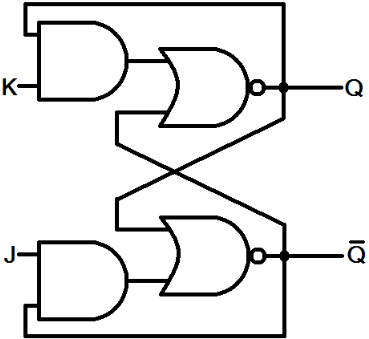

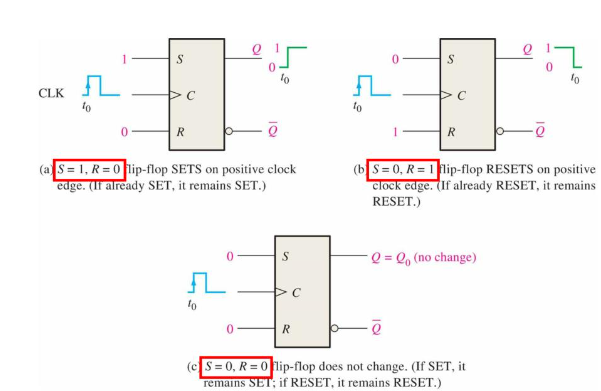

Larawan 2: JK Flip-Flop Truth Table

JK Flip-Flop Truth Table Analysis

Ang talahanayan ng katotohanan ng JK flip-flop ay isang pangunahing tool para sa paggunita kung paano ito tumugon sa iba't ibang mga signal ng pag-input na naka-sync na may mga pulso ng orasan.Ang talahanayan na ito ay tumutulong sa parehong pagdidisenyo at pag-aayos ng mga digital na circuit sa pamamagitan ng pagpapakita kung paano nagbabago ang mga output ng flip-flop batay sa iba't ibang mga kondisyon ng pag-input.

• Parehong J at K Mababa (j = 0, k = 0): Kapag ang parehong mga input ay 0, ang flip-flop ay humahawak sa kasalukuyang estado nito.Mataas man o mababa ang Q, mananatili itong hindi nagbabago.Ito ay kapansin-pansin para sa mga circuit kung saan nais ang matatag na pagpapanatili ng data, tulad ng mga elemento ng in-memorya, kung saan ang pagpapanatili ng kasalukuyang estado ay angkop hanggang sa isang tiyak na pagbabago ay na-trigger.

• j Mataas, K mababa (j = 1, k = 0): Kapag ang j ay 1 at k ay 0, ang flip-flop ay nagtatakda ng output Q hanggang mataas (1).Ang kondisyon ng setting na ito ay kapaki -pakinabang sa mga aplikasyon na nangangailangan ng isang tumpak na pag -trigger upang maisaaktibo ang isang operasyon, tulad ng pag -on sa isang aparato o pagsisimula ng isang pagkakasunud -sunod sa isang logic circuit.

• J Mababa, K Mataas (J = 0, K = 1): Sa J sa 0 at K sa 1, ang pag-reset ng flip-flop, na ginagawang mababa ang q (0).Ang pag -reset ng function na ito ay seryoso sa mga system na kailangang bumalik sa isang default na estado, tulad ng pag -clear ng data o pagsisimula ng isang proseso.

• Parehong j at k mataas (j = 1, k = 1): Kapag ang parehong mga input ay mataas, ang flip-flop toggles ang estado nito.Kung ang Q ay mataas, ito ay nagiging mababa, at kung ang Q ay mababa, lumipat ito sa mataas.Ang pag -uugali na ito ay malaki para sa mga aparato na kailangang mag -alternate sa pagitan ng mga estado, tulad ng sa dalas ng mga divider o counter.

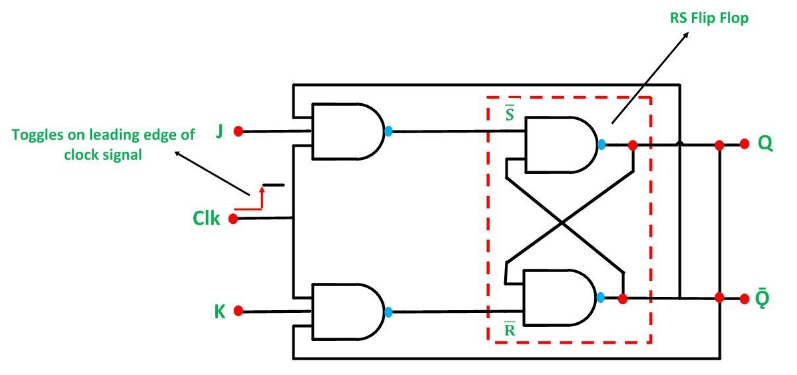

Larawan 3: JK Latch

Mga pananaw sa JK Latch Operation at Gamit

Ang JK latch ay nagpapatakbo ng katulad sa JK flip-flop ngunit nang walang pangangailangan para sa isang signal ng orasan.Sa halip na maghintay para sa isang gilid ng orasan, ang JK latch ay patuloy na tumugon sa mga pagbabago sa pag-input, ginagawa itong "sensitibo sa antas."Nangangahulugan ito na hangga't ang mga input (J at K) ay matatag, ang output ay magbabago sa real-time, na nag-aalok ng agarang puna batay sa mga kondisyon ng pag-input.

Hindi tulad ng gilid na naka-trigger na JK flip-flop, na nag-update lamang ng output nito kapag nagbabago ang signal ng orasan (mula sa mababa hanggang mataas o kabaligtaran), ang JK latch ay nag-aayos ng output nito kaagad bilang shift ng mga input.Ang pare-pareho, real-time na pagtugon ay mahalaga sa mga senaryo kung saan nais ang agarang pagkilos nang walang pagkaantala na dulot ng pag-synchronise ng orasan.

Mga Filter ng ingay: Sa mga digital na circuit na kailangang mabilis na i -filter ang hindi ginustong ingay, ang instant reaksyon ng JK Latch sa mga pagbabago sa pag -input ay maimpluwensyahan.Dahil hindi ito maghintay para sa isang pulso ng orasan, maaari itong ayusin ang output sa sandaling napansin ang ingay, na pumipigil sa mga pagkaantala sa pagwawasto ng signal.

Simpleng mga elemento ng memorya: Ang JK latch ay maaaring magsilbing isang pangunahing yunit ng memorya sa mga system na hindi nangangailangan ng kumplikado, na -clocked na kontrol.Dahil pinapanatili ng latch ang output na matatag hangga't hindi nagbabago ang mga input, epektibong hawak nito ang kasalukuyang estado, na kapaki -pakinabang para sa mga circuit na kailangang mapanatili ang impormasyon nang walang overhead ng mga operasyon na na -clocked.

Larawan 4: Pagtatasa ng Diagram ng Timing para sa JK Flip-Flop

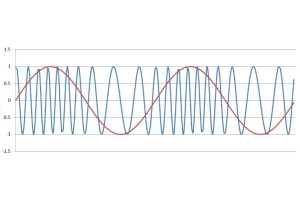

Sinusuri ang diagram ng tiyempo ng JK flip-flops

Ang isang diagram ng tiyempo ng JK flip-flop ay nagbibigay ng isang visual breakdown kung paano tumugon ang output sa iba't ibang mga input, na naka-synchronize sa mga paglilipat ng pulso ng orasan.Ang diagram na ito ay nagpapakita ng ugnayan sa pagitan ng signal ng orasan (CLK) at ang mga input (J at K), at kung paano nila kolektibong naiimpluwensyahan ang mga output (Q at Q ').Tumutulong ito upang mapa ang pag-uugali ng flip-flop sa mga sunud-sunod na estado, na ginagawang mas madaling maunawaan ang operasyon nito.

Una, ang diagram Mga highlight na ang mga output ay na -update lamang sa tumataas o bumabagsak na mga gilid ng tibok ng orasan.Ang tampok na ito, na kilala bilang Edge-Triggering, ay nangingibabaw sa operasyon ng JK flip-flop.Ipinapakita nito na kahit na ang pagbabago ng J at K, ang output ay nananatiling hindi nagbabago hanggang sa mangyari ang gilid ng orasan, tinitiyak ang mahuhulaan at matatag na mga paglilipat.

Pagkatapos, habang ang mga mapa ng diagram ay ang mga pagkakaiba -iba ng mga input j at k, biswal ito Nagpapakita kung paano nakakaapekto ang bawat kumbinasyon ng input sa output. Halimbawa, kapag ang parehong J at K ay mababa (0), ang output ay humahawak sa kasalukuyang estado nito.Kapag mataas si J at mababa ang k, nakatakda ang output.Ang malinaw na visual na representasyon na ito ay tumutulong sa mga gumagamit na maunawaan kung paano tumugon ang flip-flop sa iba't ibang mga kumbinasyon ng input sa real-time.

Sa wakas, Ang diagram ng tiyempo ay malinaw na nagpapakita ng mga paglilipat sa pagitan ng iba't ibang mga estado ng output, kung may hawak, setting, pag -reset, o toggling.Ang bawat pagbabago ng estado ay nakatali nang direkta sa mga kondisyon ng pag-input at gilid ng orasan, na nagpapakita ng isang sanhi-at-epekto na relasyon na focal para sa pagdidisenyo at pag-aayos ng mga circuit.

Maraming nalalaman mga aplikasyon ng JK flip-flops

Ang JK flip-flops ay mga pangunahing sangkap sa isang malawak na hanay ng mga digital system, na kilala para sa kanilang kakayahang umangkop at pagiging maaasahan.Ang kanilang kakayahang hawakan ang mga kumplikadong operasyon ng lohika ay ginagawang kinakailangan sa kanila sa ilang mga pangunahing aplikasyon, kabilang ang:

Larawan 5: Pag -iimbak ng memorya

Ang mga JK flip-flops ay karaniwang ginagamit upang mag-imbak ng mga indibidwal na piraso ng data, na ginagawa silang mga elemento ng pundasyon sa mga arrays at rehistro ng memorya.Ang bawat flip-flop ay may hawak ng isang bit, tinitiyak ang maaasahang pag-iimbak ng data, na kapaki-pakinabang sa disenyo ng mas malaking mga sistema ng memorya.

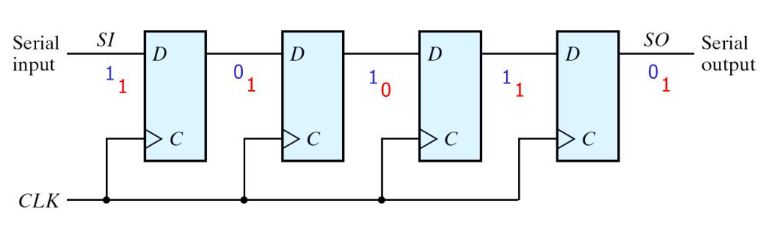

Larawan 6: Mga counter at mga rehistro ng shift

Ang JK flip-flops ay pabago-bago sa mga operasyon ng pagkakasunud-sunod.Malawakang ginagamit ang mga ito sa mga counter para sa pagbibilang ng mga kaganapan o pulses at sa mga rehistro ng shift para sa pag -convert ng mga serial data sa magkakatulad na mga format.Ginagawa itong kapaki -pakinabang sa pamamahala at pagmamanipula ng data sa iba't ibang yugto ng isang proseso, tulad ng sa mga sistema ng komunikasyon.

Larawan 7: Frequency Division

Sa pagproseso ng signal, ang mga JK flip-flops ay madalas na ginagamit para sa dalas ng dibisyon.Sa pamamagitan ng pag -toggling ng kanilang estado sa bawat pulso ng orasan, hinati nila ang dalas ng signal ng pag -input, na lumilikha ng isang mabagal, mas pinamamahalaan na signal ng orasan.Ito ay kapansin -pansin sa mga aplikasyon tulad ng pamamahala ng signal ng orasan, kung saan nais ang control control.

Larawan 8: Pag -synchronise

Ang JK flip-flops ay tumutulong sa pag-synchronize ng maraming mga digital na proseso sa pamamagitan ng pagtiyak na ang iba't ibang mga bahagi ng isang sistema ay gumana nang magkasama sa isang coordinated na paraan.Tinitiyak nila na ang iba't ibang mga sangkap ay tumugon nang tama sa mga naka -time na signal, na pinapanatili ang pag -sync ng buong sistema.

Larawan 9: JK Flip-Flop: Edge-triggered at level-triggered

Iba't ibang uri ng JK flip-flops

Ang JK flip-flops ay magagamit sa dalawang pangunahing uri: Edge-triggered at level-triggered, bawat isa ay dinisenyo para sa iba't ibang mga kinakailangan sa pagpapatakbo.

Edge-triggered JK flip-flops: Baguhin lamang ang kanilang estado sa mga tiyak na puntos - kapag ang mga paglilipat ng signal ng orasan mula sa mababa hanggang mataas (tumataas na gilid) o mataas hanggang mababa (bumabagsak na gilid).Ang katangian na ito ay ginagawang perpekto para sa mga system kung saan ang tumpak na tiyempo ay igiit.Dahil ang mga pagbabago sa estado ay nangyayari nang eksakto sa gilid ng orasan, tinitiyak ng mga flip-flop na ito ang lahat ng mga pag-update na nangyayari sa pag-sync sa tibok ng orasan.Ang mahuhulaan na pag -uugali na ito ay pabago -bago sa mahigpit na kinokontrol na mga kapaligiran tulad ng mga digital na orasan, rehistro, at pinaka -sunud -sunod na mga circuit.Dito, ang tiyempo ng bawat pagbabago ay seryoso sa pagpapanatili ng katatagan ng system at tinitiyak na ang mga operasyon ay naka -synchronize.

Level-triggered JK flip-flops: Iba -iba ang gumana, tumutugon sa signal ng pag -input hangga't ang signal ng orasan ay nasa isang partikular na antas - mataas man o mababa.Hindi sila naghihintay para sa isang tiyak na paglipat ng orasan.Sa halip, hangga't ang pag-input ay nakakatugon sa mga kinakailangang kondisyon, ang flip-flop ay magbabago ng mga estado.Ang pag-uugali na ito ay ginagawang mas mahusay na angkop sa antas ng mga flip-flop para sa mga asynchronous system, kung saan ang mga input ay maaaring hindi magkahanay sa isang regular na tibok ng orasan.Nagbibigay ang mga ito ng kakayahang umangkop sa mga system kung saan ang mga input ay hindi mahuhulaan o dumating sa hindi regular na agwat, tulad ng sa ilang mga gawain sa pagproseso ng signal o mga sistema ng pagsubaybay na dapat agad na gumanti sa pagbabago ng mga input.

Kalamangan at kahinaan ng JK flip-flop

Nag-aalok ang JK Flip-Flops ng maraming mga benepisyo ngunit kasama rin ang ilang mga trade-off na kailangang maingat na timbangin kapag nagdidisenyo ng mga digital system.

|

Mga kalamangan |

|

|

Versatility |

Ang JK flip-flops ay lubos na nababaluktot at maaari

gagamitin sa iba't ibang mga digital circuit tulad ng imbakan ng memorya, counter, at

mga control system.Maaari silang mag -toggle, itakda, o i -reset batay sa iba't ibang input

mga kondisyon, na ginagawang angkop para sa isang malawak na hanay ng mga application na

nangangailangan ng tumpak na kontrol sa mga paglilipat ng estado. |

|

Mekanismo ng pagwawasto sa sarili |

Isa sa mga tampok na standout ng JK

Ang Flip-Flops ay ang kanilang built-in na feedback loop, na tumutulong sa tama na lohikal

Mga estado na dinamikong.Tinitiyak ng pagwawasto sa sarili na nananatili ang circuit

matatag sa panahon ng operasyon, kahit na ang mga input ay mabilis na nagbabago. |

|

Pag -iwas sa kondisyon ng lahi |

Hindi tulad ng mas simpleng flip-flops, JK flip-flops

ay dinisenyo upang maiwasan ang mga kondisyon ng lahi - mga situation kung saan nagiging output

hindi matatag dahil sa magkasalungat na mga signal ng pag -input.Ang kakayahang mapanatili

Ang pare -pareho na output, kahit na sa ilalim ng mabilis at sunud -sunod na mga pagbabago sa pag -input, ay nagpapabuti sa

pagiging maaasahan ng circuit. |

|

Cons |

|

|

Kumplikadong disenyo |

Ang JK flip-flops ay mas kumplikado kaysa sa

Pangunahing Flip-Flops.Ang kanilang disenyo ay nangangailangan ng karagdagang mga gate ng lohika at pag -input

pagsubaybay, na maaaring gawing mas mahirap ang disenyo ng circuit at

Pag -troubleshoot, lalo na sa mga system kung saan ginustong ang pagiging simple. |

|

Pagkaantala ng pagpapalaganap |

Ang panloob na gating na ginamit upang pamahalaan ang estado

Ang mga paglilipat ay nagpapakilala ng pagkaantala sa kung gaano kabilis ang mga signal ay maaaring maproseso.Sa

Mga application na high-speed, ang pagkaantala na ito ay maaaring makaapekto sa pangkalahatang tiyempo at mabagal

Ang pagganap ng circuit. |

|

Mas mataas na pagkonsumo ng kuryente |

Dahil sa kanilang pagiging kumplikado at ang pangangailangan na

Patuloy na subaybayan ang mga kondisyon ng pag-input, ang JK flip-flops ay kumonsumo ng higit na lakas

Kumpara sa mas simpleng flip-flops.Sa mas malalaking sistema o sensitibo sa kuryente

mga aplikasyon, ang mas mataas na demand na kapangyarihan na ito ay maaaring maging isang disbentaha |

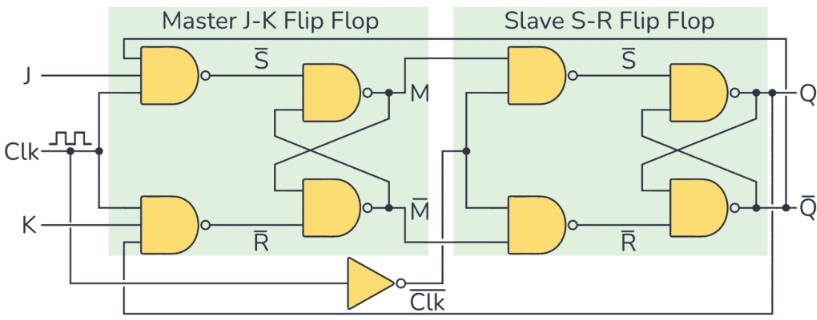

Larawan 10: Master-Slave JK Flip-Flop

Ang pag-decode ng Master-Slave JK Flip-Flop

Ang Master-Slave JK Flip-Flop ay idinisenyo upang malutas ang kondisyon ng lahi sa paligid na matatagpuan sa karaniwang JK flip-flops sa pamamagitan ng paggamit ng isang dalawang hakbang na proseso upang pamahalaan ang mga input at output nang mas mahusay.

Ang unang yugto, na tinatawag na Master Stage, kinukuha ang mga halaga ng pag -input kapag ang signal ng orasan ay umabot sa isang tiyak na gilid, alinman sa pagtaas o pagbagsak.Sa puntong ito, ang data ng pag -input ay naka -lock, nangangahulugang ang mga karagdagang pagbabago sa mga input ay hindi nakakaapekto sa nakunan na estado hanggang sa susunod na pag -ikot ng orasan.Tinitiyak ng yugtong ito na ang mga flip-flop ay nagrerehistro ng tamang pag-input nang hindi naiimpluwensyahan ng anumang kasunod na mga pagbabago sa parehong pag-ikot ng orasan.

Matapos makumpleto ang master stage, ang yugto ng alipin ay naglalaro.Ang yugtong ito ay nag -update ng output batay sa data na nakuha ng Master Stage, ngunit sa susunod na gilid ng orasan.Sa pamamagitan ng paghihiwalay ng pagkuha ng input mula sa pag -update ng output, tinitiyak ng yugto ng alipin na ang output ay nananatiling matatag hanggang sa ganap na naproseso ng master stage ang input.Pinipigilan nito ang anumang napaaga o hindi sinasadyang mga pagbabago sa output sa panahon ng pag -ikot ng orasan.

Bakit mahalaga ang master-slave configuration?

Ang proseso ng dalawang yugto ay nagpapatatag sa pagpapatakbo ng JK flip-flop, na pumipigil sa mga hindi ginustong mga oscillation o pagbabagu-bago na maaaring mangyari sa mas simpleng mga pagsasaayos, lalo na kung ang parehong mga input ay gaganapin mataas.Sa pamamagitan ng pag-decoupling ng pagproseso ng pag-input mula sa pagbabago ng output, tinitiyak ng master-slave na pagsasaayos na ang mga output ay mananatiling mahuhulaan at matatag, kahit na sa mga sitwasyon kung saan mahalaga ang tiyempo.

Pagtugon sa lahi sa paligid ng kondisyon sa JK flip-flops

Ang mga kondisyon ng lahi sa paligid ay nangyayari sa JK flip-flops kapag ang parehong mga input, J at K, ay mataas, at ang signal ng orasan ay nananatiling aktibo nang masyadong mahaba.Ito ay humahantong sa patuloy na pag -toggling ng mga output, na maaaring maging sanhi ng hindi wastong pag -uugali at guluhin ang pagiging maaasahan ng circuit.

Ang pag-setup ng Master-Slave ay gumagamit ng isang proseso ng dalawang yugto upang maiwasan ang mga isyu sa lahi.Kinukuha ng master stage ang mga halaga ng pag -input sa gilid ng orasan at i -lock ang mga ito. Ina -update ng yugto ng alipin ang mga output sa susunod na gilid ng orasan, tinitiyak na ang output ay hindi magbabago hanggang sa ganap na maproseso ang mga input.Ang pamamaraang ito ay epektibong pinipigilan ang output mula sa pag -toggling nang hindi mapigilan, kahit na ang mga input ay mananatiling mataas para sa isang pinalawig na panahon.

Ang isa pang pamamaraan upang maiwasan ang mga kondisyon ng lahi sa paligid ay ang pag-aayos ng tagal ng tibok ng orasan.Sa pamamagitan ng paggawa ng tibok ng orasan na mas maikli kaysa sa pagkaantala ng pagpapalaganap ng flip-flop, masisiguro mong hindi magbabago ang estado nang higit sa isang beses sa loob ng parehong pag-ikot ng orasan.Pinipigilan nito ang flip-flop mula sa pag-toggling nang paulit-ulit sa isang solong pag-ikot, na nagpapatatag ng output.

Dinamika ng paglipat sa JK flip-flops

Ang paglipat ng pag-uugali ng isang JK flip-flop ay higit sa lahat ay hinihimok ng tiyempo ng signal ng orasan at ang mga antas ng pag-input (J at K).Ang flip-flop ay nagbabago ng estado batay sa mga input na naroroon sa positibong gilid ng signal ng orasan.Sa mapanganib na sandaling ito, sinusuri ng flip-flop ang mga input at ina-update nang naaayon ang output nito.

Kapag ang signal ng orasan ay tumama sa tumataas na gilid, binabasa ng JK flip-flop ang kasalukuyang mga estado ng mga input ng J at K.Depende sa kanilang mga halaga, ang flip-flop ay maaaring hawakan, itakda, i-reset, o i-toggle ang output nito.

Mga digital na orasan: Ang katumpakan ay ang lahat sa mga digital na orasan, at ang JK flip-flops ay tumutulong na mapanatili ang katumpakan na ito sa pamamagitan ng pagtiyak na ang mga pagbabago ng estado ay nangyayari lamang sa tumpak na mga agwat ng orasan.

Sequential Logic Tester: Sa mga system na sumusubok sa pag-andar ng mga lohika circuit, ang JK flip-flops ay may papel sa pagpapatunay na ang bawat sangkap ay tumugon nang tama sa mga tiyak na nag-time na signal.

Iba pang mga sistema ng sensitibo sa oras: Sa iba't ibang mga digital na aplikasyon kung saan mapanganib ang tiyempo, tulad ng mga sistema ng komunikasyon o mga yunit ng pagproseso ng data, tinitiyak ng JK flip-flop na ang mga paglilipat ng estado ay nagaganap sa pag-sync sa orasan, na pumipigil sa mga error sa tiyempo.

Konklusyon

Ang JK flip-flop ay nakatayo bilang isang panghuli elemento sa disenyo ng digital circuit, na nag-aalok ng isang timpla ng maraming kakayahan at katumpakan na desperado para sa isang malawak na hanay ng mga aplikasyon na nagmula sa pag-iimbak ng memorya hanggang sa dalas ng dibisyon at pag-synchronise ng mga digital na proseso.Ang kakayahang mapagaan ang mga kondisyon ng lahi sa pamamagitan ng mga makabagong mga pagsasaayos tulad ng pag-aayos ng master-alipin ay binibigyang diin ang kakayahang umangkop sa paglutas ng mga likas na hamon sa disenyo.Pantay-pantay, ang malubhang papel ng flip-flop sa pagtiyak ng tumpak na mga paglilipat ng estado ay nagtatampok ng kinakailangang kalikasan sa paglikha at pagpapanatili ng maaasahan at mahusay na mga digital na sistema.Tulad ng pagsulong ng teknolohiya, ang mga umuusbong na disenyo at aplikasyon ng JK flip-flop ay patuloy na susi sa pagtulak sa mga hangganan ng digital electronics patungo sa mas sopistikado at matatag na mga arkitektura.

Madalas na Itinanong [FAQ]

1. Ano ang mga aplikasyon ng JK flip flop?

Ang JK flip-flop ay ginagamit nang malawak sa digital electronics para sa iba't ibang mga gawain:

Mga Application sa Timing: Maaari itong magsilbing elemento ng pagkaantala o isang timer kapag konektado sa ilang mga pagsasaayos.

Mga counter at rehistro: Sa pamamagitan ng pag -iikot ng estado nito sa bawat pulso ng orasan, ginagamit ito sa pagdidisenyo ng iba't ibang mga counter at mga rehistro ng shift na panghuli sa sunud -sunod na mga circuit circuit.

Imbakan ng memorya: Nagbibigay ito ng isang pangunahing yunit ng imbakan ng memorya, kapaki -pakinabang sa pag -iimbak ng mga bits sa mga aplikasyon ng computational.

2. Paano gumagana ang isang JK flip-flop na may isang talahanayan ng katotohanan?

Ang isang JK flip-flop ay may dalawang input (J at K) at isang signal ng orasan.Ang operasyon nito ay nag -iiba batay sa mga estado ng pag -input, na naka -synchronize sa orasan:

• j = 0, k = 0: Hindi nagbabago ang output.

• j = 0, k = 1: Ang output ay nag -reset sa 0.

• j = 1, k = 0: Ang output ay nakatakda sa 1.

• j = 1, k = 1: Ang mga output toggles (i.e., kung ito ay 0, nagiging 1 at kabaligtaran).

3. Ano ang JK flip flop at gumagana ba ito?

Pinagsasama ng isang JK flip-flop ang mga katangian ng SR at T flip-flops.Iniiwasan nito ang kondisyon na "ipinagbabawal" na nakikita sa SR flip-flops sa pamamagitan ng paggamit ng mga input ng JK na epektibo:

Ang estado ng flip-flop ay kinokontrol ng mga input j at k, na matukoy kung ang output ay dapat hawakan, i-reset, itakda, o toggle, kasabay ng pagtaas o pagbagsak ng gilid ng tibok ng orasan.

4. Ano ang mga aplikasyon ng mga latch at flip-flops?

Imbakan ng data: Ang mga latch at flip-flops ay seryoso para sa pag-iimbak ng data sa loob ng mga rehistro at mga arrays ng memorya.

Frequency Division: Ginamit sa dalas ng mga divider dahil sa kanilang kakayahang baguhin ang mga estado sa mga gilid ng orasan, na humihinto sa dalas sa bawat yugto sa isang serye.

Mga makina ng estado: Pangunahing sa pagdidisenyo ng mga hangganan na makina ng estado na ginagamit upang maipatupad ang sunud -sunod na lohika at control circuit.

Debouncing: Ginamit upang patatagin ang mga signal mula sa mga mekanikal na switch at pindutan, tinitiyak ang solong, malinis na mga paglilipat.

5. Ano ang ginagamit ng mga flip-flops?

Imbakan ng binary: Ang bawat flip-flop ay nag-iimbak ng isang piraso ng data, na ginagawa silang mga bloke ng pagbuo para sa mga aparato ng imbakan ng binary.

Clock Dividers: Hinahati nila ang dalas ng pag -input ng orasan ng dalawa, kapaki -pakinabang sa mga digital na orasan at mga aplikasyon ng tiyempo.

Tungkol sa atin

ALLELCO LIMITED

Magbasa nang higit pa

Mabilis na pagtatanong

Mangyaring magpadala ng isang pagtatanong, tutugon kami kaagad.

JRC4558 OP-AMP: Mga tampok, pagtutukoy, at mga aplikasyon

sa 2024/09/18

330 ohm risistor at mga code ng kulay

sa 2024/09/13

Mga sikat na post

-

Ano ang GND sa circuit?

sa 1970/01/1 3036

-

RJ-45 Gabay sa Konektor: RJ-45 Mga Kulay ng Kulay ng Konektor, Mga Scheme ng Wiring, R-J45 Application, RJ-45 Datasheets

sa 1970/01/1 2606

-

Mga Uri ng Connector ng Fiber: SC vs LC at LC vs MTP

sa 1970/01/1 2161

-

Pag -unawa sa mga boltahe ng supply ng kuryente sa electronics VCC, VDD, VEE, VSS, at GND

sa 0400/11/13 2064

-

Paghahambing sa pagitan ng DB9 at RS232

sa 1970/01/1 1788

-

Ano ang baterya ng LR44?

Ang kuryente, na nasa buong lakas na iyon, tahimik na sumisid sa bawat aspeto ng ating pang-araw-araw na buhay, mula sa mga walang kabuluhan na mga gadget hanggang sa nagbabantang kagamitan sa medikal, gumaganap ito ng isang tahimik na papel.Gayunpaman, ang tunay na pagkakahawak ng enerhiya na ito, lalo na kung paano mag -imbak at mahusay na ma -output ito, ay hindi madaling gawain.Ito ay labag sa...sa 1970/01/1 1754

-

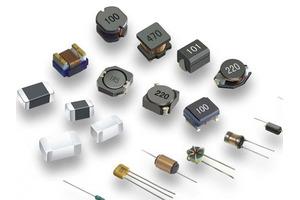

Pag -unawa sa mga batayan: paglaban sa inductance, atcapacitance

Sa masalimuot na sayaw ng elektrikal na engineering, isang trio ng mga pangunahing elemento ay tumatagal ng entablado: inductance, paglaban, at kapasidad.Ang bawat isa ay nagdadala ng mga natatanging katangian na nagdidikta sa mga dynamic na ritmo ng mga electronic circuit.Dito, nagsisimula kami sa isang paglalakbay upang matukoy ang mga kumplikado ng mga sangkap na ito, upang alisan ng takip ang ...sa 1970/01/1 1704

-

CR2430 Baterya Comprehensive Guide: Mga pagtutukoy, aplikasyon at paghahambing sa mga baterya ng CR2032

Ano ang baterya ng CR2430?Mga benepisyo ng mga baterya ng CR2430PamantayanCR2430 Mga Application ng BateryaKatumbas ng CR2430CR2430 kumpara sa CR2032Laki ng baterya CR2430Ano ang hahanapin kapag bumili ng CR2430 at katumbasData Sheet PDFMadalas na nagtanong Ang mga baterya ay ang puso ng maliit na elektronikong aparato.Kabilang sa maraming mga uri na magagamit, ang mga cell ng barya ay naglalaro n...sa 1970/01/1 1640

-

Ano ang RF at bakit natin ito ginagamit?

Ang teknolohiya ng Radio Frequency (RF) ay isang pangunahing bahagi ng modernong wireless na komunikasyon, na nagpapagana ng paghahatid ng data sa mga malalayong distansya nang walang pisikal na koneksyon.Ang artikulong ito ay sumasalamin sa mga pangunahing kaalaman ng RF, na nagpapaliwanag kung paano ginagawang posible ang electromagnetic radiation (EMR).Susuriin namin ang mga prinsipyo ng EMR, a...sa 1970/01/1 1618

-

Komprehensibong gabay sa HFE sa mga transistor

Ang mga transistor ay mga mahahalagang sangkap sa mga modernong elektronikong aparato, pagpapagana ng pagpapalakas at kontrol ng signal.Ang artikulong ito ay sumasalamin sa kaalaman na nakapalibot sa HFE, kasama na kung paano pumili ng halaga ng HFE ng transistor, kung paano makahanap ng HFE, at ang pakinabang ng iba't ibang uri ng mga transistor.Sa pamamagitan ng aming paggalugad ng HFE, nakakaku...sa 5600/11/13 1561